JAXA-QTS-2220 18 March 2025

# CRYSTAL OSCILLATORS, HIGH RELIABILITY, SPACE USE, GENERAL SPECIFICATION FOR

Japan Aerospace Exploration Agency

This document is the English version of JAXA QTS/ADS which was originally written and authorized in Japanese and carefully translated into English for international users. If any question arises as to the context or detailed description, it is strongly recommended to verify against the latest official Japanese version.

The release date of the English version of this specification: 8 September 2025

| JAXA-QTS-22  | 20 |

|--------------|----|

| 18 March 202 | 5  |

#### J A X A Parts Specification

| Pag  | е |

|------|---|

| 1 44 | _ |

– i –

#### Revision history

| Rev. | Date            | Description |

|------|-----------------|-------------|

| NC   | 18 Mar.<br>2025 | Original    |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

|      |                 |             |

#### Contents

| 1. GE  | NERAL                                                                         | 1 |

|--------|-------------------------------------------------------------------------------|---|

| 1.1    | Scope                                                                         | 1 |

| 1.2    | Definition of Terms                                                           | 1 |

| 1.3    | Part Number                                                                   | 1 |

| 1.3    | .1 Individual Identification                                                  | 1 |

| 1.3    | 3.2 Device Type                                                               | 1 |

| 1.3    | 3.3 Package Configuration                                                     | 2 |

| 1.3    | .4 Lead Material and Finish                                                   | 2 |

| 1.3    | 5.5 Radiation Hardness (Total Dose Hardness)                                  | 2 |

| 1.3    | 6.6 Nominal Frequency2                                                        | 2 |

| 2. API | PLICABLE DOCUMENTS                                                            | 3 |

| 2.1    | Applicable Documents                                                          | 3 |

| 2.2    | Reference Documents                                                           | 3 |

| 2.3    | Order of Precedence                                                           | 1 |

| 2.4    | Design Specification and Detail Specification                                 | 4 |

| 2.4    | .1 Detail Specification Number                                                | 4 |

| 2.4    | .2 Revision letter of Detail Specification                                    | 5 |

| 2.4    | .3 Independency of Detail Specification                                       | 5 |

| 2.4    | .4 Formats of Design Specification and Detail Specification                   | 5 |

| 3. RE  | QUIREMENTS                                                                    | 5 |

| 3.1    | Certification                                                                 | 5 |

| 3.1    | .1 Qualification Coverage                                                     | 5 |

| 3.1.   | .2 Initial Qualification                                                      | 5 |

| 3.1.   | .3 Retention of Qualification                                                 | 3 |

| 3.1.   | .4 Effective Period of Qualification                                          | 3 |

| 3.1    | .5 Requalification                                                            | 3 |

| 3.2    | Quality Assurance Program6                                                    | 3 |

| 3.2    | 2.1 Establishment of a Quality Assurance Program6                             | 3 |

| 3.2    | 2.2 TRB Formation6                                                            | 3 |

| 3.3    | Design and Construction                                                       | 3 |

| 3.3    | .1 Operating Temperature                                                      | 7 |

| 3.3    | 3.2 Substrates                                                                | 7 |

| 3.3    | 3.3 Metallization                                                             | 3 |

| 3.3    | .4 Mounted Elements                                                           | 9 |

| 3.3    | 5.5 Organic and Polymeric Materials10                                         | C |

| 3.3    | Mounting Materials for Substrates, Semiconductor Chips and Passive Elements10 | C |

| 3.3    | 1.7 Internal Lead Wires10                                                     | ) |

| 3.3    | 3.8 Package                                                                   | 1 |

| 3.4    | Marking13                                                                     | 3 |

| 3.4    | .1 Marking Items1                                                             | 3 |

| 3.4    | .2 Marking Location and Layout13                                              | 3 |

| 3.4    | .3 Marking Option13                                                           | 3 |

| 3.4    | .4 Exemption of Marking Items14                                               | 4 |

| 3.5    | Radiation Hardness14                                                          | 4 |

|        |                                                                               |   |

| JAXA-QTS-2220 | JAXA                | Dogo | 1     |

|---------------|---------------------|------|-------|

| 18 March 2025 | Parts Specification | Page | - 1 - |

## CRYSTAL OSCILLATORS, HIGH RELIABILITY, SPACE USE, GENERAL SPECIFICATION FOR

#### GENERAL

#### 1.1 Scope

This specification establishes the general requirements for space use, high reliability, crystal oscillators (hereinafter referred to as "crystal oscillator") used for electronic equipment installed on spacecrafts.

#### 1.2 Definition of Terms

The definitions for terms and symbols used herein are provided in paragraph 6.1 and appendixes of this specification, JAXA-QTS-2000, MIL-STD-883, MIL-HDBK-1331, MIL-STD-202 and MIL-PRF-55310.

#### 1.3 Part Number

An example of the part number of crystal oscillator is shown below. The details shall be specified in the detail specification.

#### Example:

| JAXA (1) <u>22</u> | <u>:20/101                                  </u> | <u>1</u>         | <u>CB</u>         | <u>C</u>          | <u>R</u>          | <u>100M0000</u>   |

|--------------------|--------------------------------------------------|------------------|-------------------|-------------------|-------------------|-------------------|

| In                 | idividual                                        | Device           | Package           | Lead material     | Radiation         | Nominal           |

| lc                 | dentification                                    | type             | configuration     | and finish        | hardness          | frequency         |

| (para              | graph 1.3.1) (p                                  | paragraph 1.3.2) | (paragraph 1.3.3) | (paragraph 1.3.4) | (paragraph 1.3.5) | (paragraph 1.3.6) |

Note: (1) "JAXA" indicates the common part for space use and may be abbreviated to "J."

#### 1.3.1 Individual Identification

Individual identification shall be individual number specified in the detail specification. Individual identification shall be indicated by a three-digit number. First digit identifies certified manufacturer and shall be provided by Japan Aerospace Exploration Agency (hereinafter referred to as "JAXA") and last two numbers shall be provided by certified manufacturer. Certified manufacturer shall specify provision rule and list of individual identification in quality assurance program plan.

#### 1.3.2 Device Type

The device type shall be the number assigned to the individual device type in the detail specification and shall be a one-digit number from 1 to 9.

| JAXA-QTS-2220 | JAXA                | Dogo | 0   |

|---------------|---------------------|------|-----|

| 18 March 2025 | Parts Specification | Page | -2- |

#### 1.3.3 Package Configuration

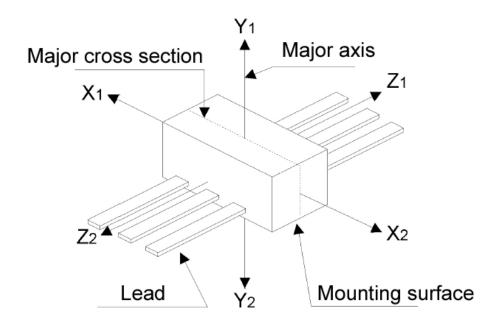

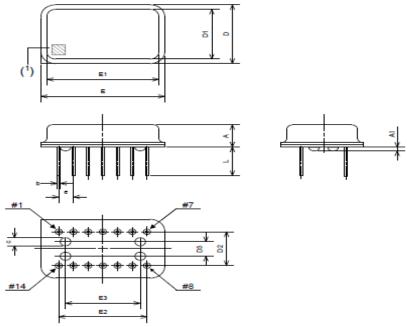

The package configuration shall be designated by two capital letters. Details shall be specified in appendix F, the detail specification and the design specification.

#### 1.3.4 Lead Material and Finish

The lead material and finish identification shall be designated by a capital letter as follows.

| Finish letter (1) | <u>Lead material</u> | <u>Finish</u>        |

|-------------------|----------------------|----------------------|

| С                 | Type A, B or C       | Gold plating         |

| Z                 | As specified in      | As specified in      |

|                   | detail specification | detail specification |

Note: (1) Finish letter "X" may be used in the detail specifications when all of the lead materials and finishes C or Z are applicable. However, the actual lead material and finish letter shall be marked on the product and its package, and the letter "X" shall not be marked.

#### 1.3.5 Radiation Hardness (Total Dose Hardness)

The radiation hardness (total dose hardness) shall be identified by a single capital letter and indicates the radiation hardness assurance level. The designator shall be used for the inspection lots that have passed the radiation hardness test (total dose test) of the subgroup 2, radiation hardness (total dose), qualification test and quality conformance inspection specified in appendix C of this specification, and shall be used for the inspection lots that have passed the radiation hardness test (total dose test) of lot evaluation test for semiconductor chips.

| <u>Letter</u> | Radiation hardness assurance level |

|---------------|------------------------------------|

| R             | 1000 Gy (Si) {1x10⁵ rad (Si)}      |

#### 1.3.6 Nominal Frequency

Nominal frequency shall be specified in detail specification.

Nominal frequency shall be identified by a single capital letter (K, M and G) indicating the frequency range and numbers indicating significant digits.

- a) When the frequency is greater than or equal to 1,000Hz and less than one megahertz (MHz), the letter "K" shall be used.

- b) When the frequency is greater than or equal to one MHz, the letter "M" shall be used.

- c) When the frequency is greater than or equal to one gigahertz (GHz), the letter "G" shall be used.

All digits before and after the letter (K, M, G) shall represent significant digits.

| JAXA-QTS-2220 | JAXA                | Page  | _ 3 _ |

|---------------|---------------------|-------|-------|

| 18 March 2025 | Parts Specification | i age |       |

#### 2. APPLICABLE DOCUMENTS

#### 2.1 Applicable Documents

The documents listed below form a part of this specification to the extent specified herein. These documents are the latest issues available at the time of contract award or application.

If a specific issue needs to be used, the issue shall be specified in the detail specification.

| a) JAXA-QTS-2000    | Common Parts/Materials, Space Use, General Specification for                                                                 |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|

| b) ISO 14644-1:1999 | Cleanrooms and Associated Controlled Environments - Part 1: Classification of Air Cleanliness                                |

| c) ISO 14644-2:2000 |                                                                                                                              |

|                     | Specifications for Testing and Monitoring to Prove Continued Compliance with ISO 14644-1                                     |

| d) MIL-STD-38534    | Hybrid Microcircuits, General Specification for                                                                              |

| e) MIL-PRF-38535    | Integrated Circuits (Microcircuits) Manufacturing, General Specification for                                                 |

| f) MIL-PRF-55310    | Oscillator, Crystal Controlled, General Specification for                                                                    |

| g) MIL-STD-202      | Test Method Standard, Electronic and Electrical Component Parts                                                              |

| h) MIL-STD-750      | Test Method Standard Test Methods for Semiconductor Devices                                                                  |

| i) MIL-STD-883      | Test Methods Standard Microelectronics                                                                                       |

| j) MIL-HDBK-1331    | Handbook for Parameters to be Controlled for the Specification of Microcircuits                                              |

| k) ASTM F1192       | Standard Guide for the Measurement of Single Event Phenomena (SEP) Induced by Heavy Ion Irradiation of Semiconductor Devices |

| I) JESD57           | Test Procedure for the Management of Single-Event Effects in Semiconductor Devices from Heavy Ion Irradiation                |

| m) ESCC5000         | Generic Specification for Discrete Semiconductor                                                                             |

|                     | Components                                                                                                                   |

| n) ESCC9000         | Integrated Circuits: Monolithic and Multichip Microcircuits,                                                                 |

|                     | Wire-Bonded, Hermetically Sealed and Flip-Chip Monolithic                                                                    |

|                     | Microcircuits with Non-Organic Substrate, Hermetically and                                                                   |

| \                   | Non-Hermetically Sealed and Die                                                                                              |

| o) ECSS-Q-ST-70-60  | Qualification and Procurement of Printed Circuit Boards                                                                      |

#### 2.2 Reference Documents

The following documents are the reference documents for this specification.

- a) JAXA-QTS-2010 Integrated Circuits, High Reliability, Space Use, General Specification for

- b) JAXA-QTS-2030 Semiconductor Devices, High Reliability, Space Use, General Specification for

- c) JAXA-QTS-2040 Capacitors, Fixed, High Reliability, Space Use, General Specification for

- d) JAXA-QTS-2050 Resistors, High Reliability, Space Use, General Specification for

| 18 | March 2025     |      | Parts Specification                   | Page              | _ 2   |

|----|----------------|------|---------------------------------------|-------------------|-------|

|    |                |      |                                       |                   |       |

| e) | JAXA-QTS-2140  | Prin | ted Wiring Boards, High Reliability   | , Space Use, Ge   | neral |

|    |                | Spe  | cification for                        |                   |       |

| f) | JAXA-QTS-2070  | Cry  | stal Units, Quartz, High Reliability, | Space Use, Gen    | eral  |

|    |                | Spe  | cification for                        |                   |       |

| g) | JERG-0-035     | JAX  | A Parts Application Handbook (lim     | nited to JAXA)    |       |

| h) | JERG-0-039     | High | n Reliability Soldering Requiremen    | its               |       |

| i) | JERG-0-043     | Star | ndard for Surface Mount Soldering     | Process           |       |

| j) | JMR-012        | Elec | ctrical, Electronic, And Electromec   | hanical Parts Pro | gram  |

|    |                | Star | ndard                                 |                   |       |

| k) | ESCC3503 issue | 5 Cı | rystal Controlled Oscillators ESCC    | Generic Specific  | ation |

JAXA

Dage

4 –

#### 2.3 Order of Precedence

JAXA-QTS-2220

In the event of a conflict between requirements specified in applicable specifications, the following order of precedence shall apply.

- a) Detail specification

- b) This specification

- c) JAXA-QTS-2000

- d) Applicable documents of this specification (paragraph 2.1) (except for JAXA-QTS-2000)

#### 2.4 Design Specification and Detail Specification

a) Preparation of design specification

When manufacturer acquires certification, the manufacturer shall prepare design specification which specifies qualification coverage (including construction and design limit values) of crystal oscillator in accordance with appendix D, and shall submit the design specification attached to quality assurance program plan to qualification audit acting agency.

b) Preparation of detail specification

Certified manufacturer shall provide detail specification number in accordance with paragraph 2.4.1, prepare and establish detail specification in accordance with appendix E and submit the detail specification to qualification audit acting agency. JAXA will issue the detail specification.

#### 2.4.1 Detail Specification Number

Detail specification number shall be assigned in accordance with paragraph A.2.2.2 of JAXA-QTS-2000. An example is shown below. Individual identification shall be a three-digit number with first digit representing certified manufacturer and remaining two digits representing series number.

#### 2.4.2 Revision letter of Detail Specification

Revision letter in detail specification number shall be assigned in accordance with paragraph A.2.2.2.4 of JAXA-QTS-2000.

#### 2.4.3 Independency of Detail Specification

Detail specification shall be a stand-alone document with a unique number in accordance with paragraph 2.4.1.

#### 2.4.4 Formats of Design Specification and Detail Specification

- a) Format of design specification shall be as specified in appendix D.

- b) Format of detail specification shall be as specified in appendix E.

#### 3. REQUIREMENTS

#### 3.1 Certification

#### 3.1.1 Qualification Coverage

Qualification shall be valid for crystal oscillators that are designed within the range of designing limit values specified in the design specifications, produced by the manufacturing line that conforms to quality assurance programs. The qualification coverage shall be within the range of that are typified by evaluation elements or samples which have passed the qualification test. Within this coverage, certified manufacturer is allowed to supply qualified products in compliance with the detail specification.

#### 3.1.2 Initial Qualification

To acquire qualification of crystal oscillators in compliance with this specification, a manufacturer shall establish a quality assurance program in accordance with paragraph 3.2.1 of this specification, perform qualification tests specified in paragraph 4.6 of this specification and acquire a certification as specified in paragraph 3.4.1 of JAXA-QTS-2000. The manufacturer shall be listed on the Certified Manufacturers List of JAXA (JAXA QML).

To acquire qualification, the manufacturer shall also prepare a design specification (to be attached to quality assurance program plan) in accordance with appendix D and a detail specification in accordance with appendix E and submit them to qualification audit acting agency.

| JAXA-QTS-2220 | JAXA                | Dogo | 6   |

|---------------|---------------------|------|-----|

| 18 March 2025 | Parts Specification | Page | -6- |

#### 3.1.3 Retention of Qualification

To continue supplying crystal oscillators in accordance with this specification, certified manufacturer shall apply for QML qualification retention in accordance with paragraph 3.4.2.1 of JAXA-QTS-2000 prior to expiration date of certification period specified in paragraph 3.1.4 of this specification.

If the crystal oscillators were not manufactured during the effective period of qualification and a quality conformance inspection was not performed, certified manufacturer may apply for the retention of qualification without performing quality conformance inspection.

#### 3.1.4 Effective Period of Qualification

Effective period of qualification granted in compliance with this specification shall be three years.

#### 3.1.5 Requalification

In the case of changes affecting design limit values, functions, performance, reliability and quality of crystal oscillators, certified manufacturer shall apply for requalification in accordance with paragraph 3.4.3 of JAXA-QTS-2000.

#### 3.2 Quality Assurance Program

#### 3.2.1 Establishment of a Quality Assurance Program

To acquire a qualification in accordance with this specification, manufacturer shall establish a quality assurance program that meets the requirements specified in paragraph 3.3.1 of JAXA-QTS-2000 and this specification. The manufacturer shall establish a quality assurance program plan in accordance with paragraph 3.3.2 of JAXA-QTS-2000 and provide the plan to qualification audit acting agency for review in accordance with paragraph 3.3.6 of JAXA-QTS-2000.

#### 3.2.2 TRB Formation

To acquire a qualification for products in accordance with this specification, manufacturer shall form and operate the Technical Review Board (TRB) in accordance with paragraph 3.3.5 of JAXA-QTS-2000.

#### 3.3 Design and Construction

Design and construction of crystal oscillators shall specify materials, processes and design rules as a whole and design limit values specified for at least following items a) to f) in accordance with appendix D shall be specified in the design specification.

| JAXA-QTS-2220 | JAXA                | Dogo | 7     |

|---------------|---------------------|------|-------|

| 18 March 2025 | Parts Specification | Page | - / - |

Design and construction of each product shall be specified in the detail specification in accordance with appendix E.

Details of design specification and detail specification shall be in accordance with paragraphs 3.3.1 to 3.3.8.

- a) Operating temperature

- 1) Case temperature

- b) Substrate

- 1) Material (e.g., Alumina)

- c) Pattern formation and metallization

- 1) Minimum element spacing (spacing between conductor-to-conductor, conductor-to-resistor, resistor-to-resistor and elements)

- 2) Minimum pattern width (conductor and resistor)

- 3) Minimum and maximum length of an element (resistor)

- 4) Film forming method (thin- or thick- film)

- 5) Film material (e.g., NiCr, Ta, Au, Pd-Ag)

- 6) Trimming method

- d) Mounted elements

- 1) Type of elements (e.g., semiconductor, capacitor)

- 2) Mounting configuration (e.g., face-up, eutectic bonding and adhesion)

- 3) Mounting material (e.g., molybdenum tablet, Au-Si eutectic, solder, nonconductive or conductive adhesive)

- 4) Maximum area and weight of mounted elements

- 5) Derating of mounted elements

- e) Internal lead wires

- 1) Material (e.g., gold, aluminum)

- 2) Configuration (e.g., wire, ribbon) and dimensions

- 3) Bonding method (e.g., thermocompression, ultrasonic, parallel gap welding)

- 4) Maximum wire (or ribbon) length (or bonding spacing)

- f) Packaging

- 1) Packaging material

- 2) Package configuration (e.g., 16-pin metal flat, package)

- 3) Sealing process (e.g., welding, brazing)

- 4) Lead material and finish

#### 3.3.1 Operating Temperature

Operating temperature of crystal oscillators shall be within the case temperature range. Minimum and maximum operating temperatures shall be specified in the design specification and detail specification.

#### 3.3.2 Substrates

Unless otherwise specified in the design specification and the detail specification, thin-film ceramic substrate and thick-film ceramic substrate shall be made of alumina (Al<sub>2</sub>O<sub>3</sub>) with the minimum purity of 99.5% and 96%, respectively.

| JAXA-QTS-2220 | JAXA                | Dogo | 0   |

|---------------|---------------------|------|-----|

| 18 March 2025 | Parts Specification | Page | -8- |

#### 3.3.3 Metallization

Unless otherwise specified in the design specification and the detail specification, metallization shall meet the following requirements.

#### 3.3.3.1 Conductors

a) Thin-film conductors

Thin-film conductors on the substrates shall be designed such that, when assumed to be properly built up, the current density shall not exceed the following maximum allowable current density when operated under the worst conditions specified in the design specification and the detail specification.

| Conductor material                                              | Maximum allowable current density   |

|-----------------------------------------------------------------|-------------------------------------|

| Gold                                                            | 6x10 <sup>5</sup> A/cm <sup>2</sup> |

| Others (unless otherwise specified in the detail specification) | 2x10 <sup>5</sup> A/cm <sup>2</sup> |

- 1) Use a current value equal to the maximum continuous current (at full fanout for digital devices or at the maximum load for linear devices) or equal to the simple time-averaged current obtained at the maximum rated frequency or duty cycle with the maximum load, whichever results in the greater current value at the point(s) of the maximum current density. This current value shall be determined at the maximum recommended rating voltage(s) and with the current assumed to be uniform over the entire conductor cross-sectional area.

- 2) Use the minimum allowable metallization thickness within controls.

- 3) Use the minimum actual design metallization width (not mask widths) including appropriate allowance for narrowing or undercutting experienced in metal etching.

- 4) Areas of the barrier metals and nonconductive material shall not be included in the calculation of the metallization cross section.

- In order to compensate for reduction of the cross section due to thinning, voids or scratches, use the cross section obtained from steps 2) through

of this paragraph and multiplied by 0.75, to calculate the maximum current density.

- b) Thick-film conductors

Thick-film conductors (such as wiring by metallization and bonding pads) on substrates shall be designed such that, when assumed to be properly built up, the power loss shall not exceed 4W/cm<sup>2</sup> if the maximum design current is applied.

| JAXA-QTS-2220 | J A X A             | D    | •        |

|---------------|---------------------|------|----------|

| 18 March 2025 | Parts Specification | Page | <u> </u> |

#### 3.3.3.2 Resistors

Unless otherwise specified in the design specification and the detail specification, the maximum power consumption of resistors shall meet the following requirements.

a) Thin-film resistors

Thin-film resistors on substrates shall be designed such that, when assumed to be properly built up, the maximum power consumption shall not exceed 93W/cm<sup>2</sup>.

b) Thick-film resistors

Thick-film resistors on substrates shall be designed such that, when assumed to be properly built up, the maximum power consumption shall not exceed 7.75W/cm<sup>2</sup>.

#### 3.3.4 Mounted Elements

Mounted elements of crystal oscillator shall be selected to meet the following requirements:

a) Finished terminals

Considering the risk of whisker growth, parts with tin plating (lead containing 3 percent or less, by mass) finished terminals shall not be used in principle. When tin plating (lead containing 3 percent or less, by mass) finished terminals are used, certified manufacturer shall evaluate any risks for whisker growth and obtain a purchaser's approval. The procedures and criteria for risk evaluation shall be approved by TRB.

b) Selection of mounted elements

Mounted elements for crystal oscillator shall be selected in accordance with paragraphs 3.3.4.1 to 3.3.4.4 of this specification.

#### 3.3.4.1 Passive Elements

- a) Chip capacitors, chip resistors and chip inductors

Chip capacitors, chip resistors and chip inductors shall be selected in

accordance with paragraph A.2.4.1 of this specification and shall be specified in

the design specification and the detail specification.

- b) Quartz crystal units

Quartz crystal units shall be selected in accordance with paragraph A.2.4.2 of this specification and shall be specified in the design specification and the detail specification.

#### 3.3.4.2 Semiconductors

a) Semiconductor chips

Semiconductor chips shall be selected in accordance with requirements in appendix A and shall be specified in the design specification and the detail specification.

Surface mounting semiconductor parts

Surface mounting semiconductor parts shall be selected with reference to the

| JAXA-QTS-2220 | JAXA                | Dogo | 10            |

|---------------|---------------------|------|---------------|

| 18 March 2025 | Parts Specification | Page | _ 10 <u>_</u> |

requirements in appendix A and shall be specified in the design specification and the detail specification.

#### 3.3.4.3 Printed Wiring Boards

Printed wiring boards shall be selected in accordance with paragraph A.2.4.3 and shall be specified in the design specification and the detail specification.

#### 3.3.4.4 Other Mounted Elements

When any other mounted elements are used, the requirements for the elements shall be specified in the design specification and the detail specification.

#### 3.3.5 Organic and Polymeric Materials

When organic and polymeric materials (e.g., coatings, adhesives) are used inside a package of crystal oscillator as assembling or coating materials, they shall not exhibit blister, crack, outgas, softening, outflow or other defects under the test conditions specified in the detail specification.

Organic and polymeric materials shall be specified in the design specification and the detail specification.

3.3.6 Mounting Materials for Substrates, Semiconductor Chips and Passive Elements Glass shall not be used for mounting substrate, semiconductor chips or passive elements.

Mounting materials for substrate, semiconductor chips or passive elements shall be specified in the design specification and the detail specification.

#### 3.3.7 Internal Lead Wires

Internal lead wires or other conductors which are not in thermal contact with the substrate along the entire length shall be designed such that the maximum rated current (continuous current for direct currents, effective value for alternating currents and peak current divided by  $\sqrt{2}$  for pulsed currents) shall not exceed the maximum allowable current calculated by the following formula.

$$I = \frac{1}{128} \times K \times d^{\frac{3}{2}}$$

where, I = Maximum allowable current (A)

d = Wire diameter (mm) (When the cross section is not circular, use the diameter of a circular wire or conductor of the same cross section area)

K = A constant obtained from the length and composition of the wire or conductor as shown in Table 1.

| JAXA-QTS-2220 | JAXA                | Dogo | 11     |

|---------------|---------------------|------|--------|

| 18 March 2025 | Parts Specification | Page | - 11 - |

#### Table 1. "K" value

| Matarial  | "K" value for bond-to-bond total conductor length |                |

|-----------|---------------------------------------------------|----------------|

| Material  | Length ≤ 1.0mm                                    | Length > 1.0mm |

| Aluminum  | 22000                                             | 15200          |

| Gold      | 30000                                             | 20500          |

| Copper    | 30000                                             | 20500          |

| Silver    | 15000                                             | 10500          |

| All other | 9000                                              | 6300           |

#### 3.3.8 Package

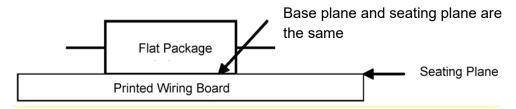

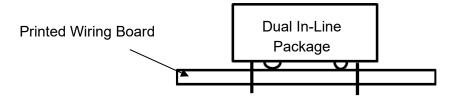

Unless otherwise specified in the detail specification, package shall be such that the leads have stress relief when mounted on printed wiring board, such as a flat package. Packages shall be selected in accordance with paragraph A.2.4.4 of this specification.

- a) Package configuration

- Qualification coverage of package configuration shall be specified in design specification in accordance with appendix D. Package configuration of each product shall be specified in detail specification in accordance with appendix E.

- b) Package material

External metal surfaces of the package shall be corrosion resistant. External leads shall meet the requirements of c) below. Nonmetallic materials of the package and coatings materials including markings shall be non-nutrient to fungus and shall not exhibit any blister, crack, outgas, softening, outflow or other defects under the test conditions specified in detail specification. Details shall be specified in the detail specification.

#### c) Lead material and finish

#### 1) Lead material

Lead material shall be one of the following types unless otherwise specified in detail specification.

#### 1.1) Type A

| Iron                             | 53% nominal             |

|----------------------------------|-------------------------|

| Nickel                           | 29±1%                   |

| Cobalt                           | 17±1%                   |

| Manganese                        | 0.65% max.              |

| Silicon                          | 0.20% max.              |

| Carbon                           | 0.06% max.              |

| Aluminum                         | 0.10% max.              |

| Magnesium                        | 0.10% max.              |

| Zirconium                        | 0.10% max.              |

| Titanium                         | 0.10% max.              |

| (The sum of aluminum, magnesium, | zirconium, and titanium |

contents shall be 0.20% as a maximum.)

| 18 March 2025  | Parts Specification         | Page           | -   |

|----------------|-----------------------------|----------------|-----|

| 4 O) T         |                             |                |     |

| 1.2) Type B    |                             |                |     |

| Nickel         |                             | 40.00% to 43.0 | 00% |

| Cobalt         |                             | 0.500% max.    |     |

| Mangan         | ese                         | 0.800% max.    |     |

| Silicon        |                             | 0.300% max     | X.  |

| Carbon         |                             | 0.100% max     | X.  |

| Aluminu        | m                           | 0.100% max     | Χ.  |

| Chrome         |                             | 0.250% max     | X.  |

| Phosphorus     |                             | 0.025% max.    |     |

| Sulfur         |                             | 0.025% max.    |     |

| Iron           |                             | Remainde       | r   |

| 1.3) Type C (0 | Copper-core, Fe-Ni52 alloy) |                |     |

| Copper (       | (core)                      | 99.96% mir     | ١.  |

| Nickel         |                             | 48% to 52%     | 6   |

| Carbon         |                             | 0.02% max      | ζ.  |

| Manganese      |                             | 0.2% to 1.0°   | %   |

| Silicon        |                             | 0.1% to 0.5°   | %   |

| Sulfur         |                             | 0.025% max     | Χ.  |

| Phospho        | orus                        | 0.025% max.    |     |

| Iron           |                             | Other          |     |

JAXA

**–** 12 **–**

#### 2) Lead Finish

JAXA-QTS-2220

Unless otherwise specified in the detail specification, lead finish shall be one of the following options from 2.1) to 2.3).

#### 2.1) Solder dip

Solder dip shall be homogeneous with the minimum thickness of  $5.08\mu m$  at the major flats of solder (Sn60 to Sn63) over a primary finish in accordance with type 2.2) below or nickel plating (with the thickness between  $2.54\mu m$  and  $7.62\mu m$ ).

#### 2.2) Gold plating

Purity of gold plating shall be a minimum of 99.7% gold (i.e., the sum of impurities and other metals shall be 0.3% as a maximum). Gold plating thickness shall be a minimum of 1.27 $\mu$ m. This finish requires electrolytic nickel or copper base plating with a thickness between 1.27 $\mu$ m and 7.62 $\mu$ m.

#### 2.3) Tin lead plating

Percentage of lead shall be between 3% and 50%. Tin lead plating thickness shall be minimum 7.62 $\mu$ m. Electroless nickel or electrolytic nickel base plating may be used for this finish. Thickness of the base plating shall be between 1.27 $\mu$ m and 8.89 $\mu$ m.

| JAXA-QTS-2220 | JAXA                | Page | 12     |

|---------------|---------------------|------|--------|

| 18 March 2025 | Parts Specification | Page | – 13 – |

#### 3.4 Marking

#### 3.4.1 Marking Items

At least the following marking items shall be specified in the detail specification.

- a) Index point (paragraph 3.4.1.1)

- b) Part number (paragraph 1.3)

- c) Inspection lot identification code (paragraph 3.4.1.2)

- d) Serial number (paragraph 3.4.1.3)

- e) Certified manufacturer's identification (paragraph 3.4.1.4)

#### 3.4.1.1 Index Point

Index point indicates the start of lead numbers or mechanical orientation and shall be shown by a stamp, tab, notch or groove, among other means. The index point shall be visible from the top when the product is mounted in a normal manner. Certified manufacturer's identification code shall not be used for this purpose.

#### 3.4.1.2 Inspection Lot Identification Code

An inspection lot identification code shall be assigned to each inspection lot (refer to 2) of (paragraph 4.3.1 l)) and shall be marked.

#### 3.4.1.3 Serial Number

A serial number shall be assigned to each crystal oscillator in inspection lot prior to screening test (refer to paragraph 4.7).

#### 3.4.1.4 Certified manufacturer's Identification

Certified manufacturer's identification shall be the certified manufacturer's name, abbreviation or trademark.

#### 3.4.2 Marking Location and Layout

Unless otherwise specified in the detail specification, part number and inspection lot identification code shall be located on the top surface of packages. Each marking item may be placed in any way as long as it satisfies the marking requirement and does not interfere with other markings.

#### 3.4.3 Marking Option

Certified manufacturer shall complete markings by the start of external visual inspection of screening test.

| JAXA-QTS-2220 | JAXA                | Dogo | _ 14 _            |

|---------------|---------------------|------|-------------------|

| 18 March 2025 | Parts Specification | Page | - 14 <del>-</del> |

#### 3.4.4 Exemption of Marking Items

When the surface area of crystal oscillator is not sufficient to place all the marking items specified in paragraph 3.4.1, marking items may be exempted in the following order or priority. Details shall be specified in detail specification.

- a) "2220-" of part number

- b) Package configuration and lead material/finish designator of part number. (In this case, both designators shall be exempted).

- c) Certified manufacturer's identification

#### 3.5 Radiation Hardness

#### 3.5.1 Total Dose Radiation Hardness

Total dose radiation hardness of crystal oscillator shall be specified in the detail specification. When total dose radiation hardness is required for semiconductor chip, the semiconductor chip shall be selected in accordance with appendix A and shall be specified in the detail specification.

#### 3.5.2 Single Event Characteristics

As for single event characteristics of crystal oscillator, characteristics selected from the following items relating to product shall be specified in the detail specification. When single event characteristics are required for semiconductor chip, the semiconductor chip shall be selected in accordance with appendix A and shall be specified in the detail specification.

- a) SEU

- b) SEL

- c) Others

#### 4. QUALITY ASSURANCE PROVISIONS

#### 4.1 General Requirements

Certified manufacturer shall be responsible for implementing quality assurance program specified in paragraph 3.2 of this specification and operating TRB.

#### 4.2 Incoming Parts and Materials Control

Incoming parts and materials shall be subject to an appropriate incoming inspection and controlled to ensure that each part and material is traceable to incoming inspection lot. Certified manufacturer shall establish and implement procedures to store and retrieve received parts and materials and to remove limited-life parts and materials.

| JAXA-QTS-2220 | JAXA                | Dogo | 45       |

|---------------|---------------------|------|----------|

| 18 March 2025 | Parts Specification | Page | <u> </u> |

#### 4.2.1 Incoming Inspection

Test items, test methods and pass/fail criteria of incoming inspection for each part and material used for crystal oscillator shall be specified in detail specification.

#### 4.2.2 Record of Incoming Parts and Materials Control

The records of incoming parts and materials shall be categorized into incoming inspection records and storage, retrieval and disposal records. These records shall include the following items as a minimum.

- a) Incoming inspection records

- 1) Part and Material name

- 2) Inspection items

- 3) Lot size

- 4) Lot identification code

- 5) Document number and established date of inspection instructions

- 6) Pass or fail of each lot and quantity of failed parts and materials

- 7) Date of inspection and name or identification code of the inspector

- b) Storage, retrieval and disposal records

- 1) Part and Material name

- 2) Storage conditions

- 3) Lot identification code

- 4) Storage date and quantity of storage materials

- 5) Retrieval date and quantity, lot identification code of finished or semi-finished products for which the part and material are used.

- 6) Disposal date and quantity

#### 4.3 Manufacturing Process Control

Certified manufacturer shall establish and maintain procedures of manufacturing processes, control parameters and methods.

#### 4.3.1 Control of Manufacturing Process Works

Certified manufacturer shall define and control each manufacturing process works including the items listed below as a minimum. Rework shall be performed in accordance with paragraph 4.3.2 of this specification. Certified manufacturer shall also establish and implement a storage method for finished or semi-finished products between each manufacturing process work.

- a) Formation of substrate lots

- 1) Formation procedure of substrate lots

- 2) Assignment of substrate lot identification codes

- b) Metallization process

- 1) Manufacturing process of thin-film substrates

- 1.1) Mask control

- 1.2) Metallization material

| JAXA-QTS-2220 | JAXA                | Dana | 46       |

|---------------|---------------------|------|----------|

| 18 March 2025 | Parts Specification | Page | <u> </u> |

- 1.3) Forming method

- 1.4) Forming conditions

- 1.5) Method and frequency of chamber cleaning

- 2) Electrolytic plating process

- 2.1) Metallization material

- 2.2) Plating solution and control of plating bath

- 2.3) Plating conditions

- 3) Manufacturing process of thick-film substrates

- 3.1) Screen control

- 3.2) Paste material

- 3.3) Forming method

- 3.4) Forming conditions

- 3.5) Furnace control

- c) Pattern formation process

- 1) Masking method

When photolithography is used, the following items on handling of photo resist shall be specified.

- 1.1) Preparation method

- 1.2) Evaluation methods for specific gravity, viscosity, solid residues and pinholes

- 1.3) Storage conditions

- 1.4) Coating conditions

- 1.5) Baking conditions

- 1.6) Exposure conditions

- 1.7) Developing conditions

- 2) Etching technique

When wet etching is used, the following items shall be specified.

- 2.1) Preparation method

- 2.2) Composition, grade, temperature, etc., of etching solution

- 2.3) Frequency of etching solution change

- 2.4) Etching conditions

- 2.5) Washing and drying

- 3) Inspection process

- 3.1) Method of visual inspection and pass/fail criteria

- d) Trimming of resistors

- 1) Trimming method and facility type

- 2) Trimming conditions

- 3) Inspection for resistance and film stability

- 4) Method of visual inspection and pass/fail criteria

- e) Scribing and substrate separation

- 1) Scribing method and conditions

- 2) Dicing method and conditions

- 3) Method of visual inspection and pass/fail criteria

- f) Formation of production lots

- 1) Formation of production lots<sup>(1)</sup>

- 2) Assignment of production lot identification code

| JAXA-QTS-2220 | JAXA                |      | 47   |

|---------------|---------------------|------|------|

| 18 March 2025 | Parts Specification | Page | -17- |

Note (1) Production lot should be prepared such that inspection sub-lots are able to be easily prepared (paragraph 4.3.1 k)).

- g) Substrate and parts mounting process

- 1) Mounting material and package material in the mounting area

- 2) Mounting structure

- 3) Mounting conditions

- 4) Visual inspection method for mounting

- 5) Control method of adhesive strength

- h) Interconnection bonding

- 1) Material

- 2) Lead type

- 3) Bonding method

- 4) Bonding conditions

- 5) Visual inspection for bonding

- 6) Nondestructive bond pull test method

- 7) Control method of bond strength

- i) Pre-seal visual inspection

- 1) Procedure and pass/fail criteria of visual inspection

- j) Sealing process

- 1) Package and sealing materials

- 2) Sealing method

- 3) Stabilization bake prior to sealing

- 4) Sealing conditions

- k) Formation of inspection sub-lots

- 1) Formation of inspection sub-lots<sup>(1)</sup>

- 2) Assignment of inspection sub-lot identification code

Note (1) Inspection sub-lots shall meet the following requirements.

- An inspection sub-lot shall consist of crystal oscillators of a single part number and single device type with identical package type and lead finish.

- ii. All products of an inspection sub-lot shall be manufactured using a single substrate lot.

- iii. Each inspection sub-lot shall consist of semiconductor chips made from a single wafer lot.

- iv. Each inspection sub-lot shall be manufactured using the same machines in each production process.

- v. The entire assembly process from assembly start (such as substrate attachment and MOSFET mounting) to package sealing shall be completed within the same 12-week period.

- vi. Each inspection lot shall consist of 500 crystal oscillators as a maximum.

- I) Formation of inspection lots

- 1) Formation of inspection lots<sup>(1)</sup>

- 2) Assignment of inspection lot identification code

Note (1) Inspection lots shall satisfy the following requirements.

i. An inspection lot shall consist of crystal oscillators of a part number with identical identification number, selected from a maximum of five

| JAXA-QTS-2220 | JAXA                | Dana | 40            |

|---------------|---------------------|------|---------------|

| 18 March 2025 | Parts Specification | Page | _ 18 <u>_</u> |

inspection sub-lots. The case configuration, package types, and lead finish shall be identical.

ii. The entire assembly process from assembly start (such as substrate attachment and MOSFET mounting) to package sealing shall be completed within the same 16-week period.

#### 4.3.2 Rework Control

When rework specified below is performed, the rework results shall be documented in records as specified in paragraph 4.3.5. Reworked products shall be clearly identifiable from other products. After final sealing, rework shall be limited to re-cleaning, correction of defective marking and lead straightening (e.g., reshaping of leads such as correction of lead tip shape which does not degrade for seal of the product.). In addition, opening operations shall not be performed after final sealing.

#### 4.3.2.1 Re-Bonding and Element Replacement

Unless otherwise specified in detail specification, re-bonding and replacement of attached elements should be allowed under the following conditions.

- a) Re-bonding shall not be performed on bonding pads that have been damaged to the extent that the top layer of metallization in the area being bonded is lifted or peeled away or the underlying metallization or substrate is exposed.

- b) The total number of re-bonding shall be limited to a maximum of 10% of the total number of bonds in the crystal oscillator. Re-bonding of wires to substrate pads or package posts for replacing elements shall not be limited to this maximum number.

- c) The total number of internal connection bonding or element replacements shall be limited to three times. Element replacements shall only be for the elements which are mounted by adhesive or solder.

#### 4.3.2.2 Rework of Conductors on Substrate

Rework shall be allowed to repair scratches, breaking, discontinuation of conductors on substrates using bonding wires or ribbons which have current capacity of 3.5 times the maximum operating load current (refer to paragraph 3.3.3). Repair shall be limited to one area per substrate area of 323mm<sup>2</sup>.

#### 4.3.2.3 Replacement of Substrates and Packages

Unless otherwise specified in the detail specification, substrates and packages of crystal oscillator shall not be replaced.

| JAXA-QTS-2220 | JAXA                | Page | 10     |

|---------------|---------------------|------|--------|

| 18 March 2025 | Parts Specification | Page | _ 19 – |

#### 4.3.3 Environmental Control

Temperature, relative humidity and dust counts shall be controlled for manufacturing processes (such as substrate manufacturing processes and assembly operations) which are significantly affected by the environments. The particle counting shall be performed in accordance with ISO 14644-1 and ISO 14644-2.

#### 4.3.4 Water Purity Control

Purity of water shall be controlled with respect to the minimum specific resistively, maximum total solids, maximum organic impurity, maximum bacteria quantity and maximum chlorine contents at room temperature.

#### 4.3.5 Records of Manufacturing Processes

Records of manufacturing processes shall be categorized as either work records for the manufacturing processes or control records for the environmental conditions. Records of manufacturing processes shall include at least the following items.

- a) Work records for the manufacturing process

- 1) Name of work

- 2) Lot identification code of materials and products (including semi-finished products)

- 3) Document number and issue date of the document that ordered the work to be performed.

- 4) Quantity of incoming and outgoing products (including semi-finished products) for each work and disposition

- 5) Date of work and name or identification code of operator

- 6) Identification of facility used

- b) Control records such as for environmental conditions

- 1) Document number and issue date of the document directing the control method

- 2) Date of measurement and name or identification code of operator

#### 4.4 Classification of Inspections and Tests

Inspections and tests shall include screening test in addition to three categories specified in paragraph 4.3 of JAXA-QTS-2000.

- a) In-process inspection

- b) Qualification test

- c) Screening test

- d) Quality conformance inspection

#### 4.5 In-Process Inspection

Certified manufacturer shall perform in-process inspections specified below during the manufacturing process of crystal oscillator to detect any failure which could seriously affect the reliability and quality of the products, assure the workmanship, and characterize

| JAXA-QTS-2220 | JAXA                | Dana | 20            |

|---------------|---------------------|------|---------------|

| 18 March 2025 | Parts Specification | Page | <b>– 20 –</b> |

properties which cannot be measured on the finished products. Test items, test methods, pass/fail criteria and sample quantity shall be shown in manufacturing process flowchart and shall be specified in detail specification.

- a) Internal visual inspection of semi-finished products (100% non-destructive or sampled inspection)

- Final visual inspection prior to sealing shall be conducted to all sample.

- b) Physical or chemical inspection of semi-finished products (sampled destructive or non-destructive inspection)

- 1) Bond pull strength test

- 2) Die shear strength test

- c) Characterization of semi-finished products (100% non-destructive or sampled inspection)

#### 4.5.1 In-Process Inspection Records

Certified manufacturer shall specify in-process inspection records in quality assurance program as specified in paragraph 3.2.1.

#### 4.6 Qualification Test

Qualification test shall be performed on the inspection lot which passed the screening test in accordance with Appendix C using evaluation elements or samples which were produced using the same design, construction, materials and manufacturing line as those to be qualified.

#### 4.6.1 Evaluation Elements or Samples

Evaluation elements or samples shall be produced using design, construction, materials and manufacturing line specified in quality assurance program and shall have sufficient functions and performance to evaluate construction and design limits of the products. Therefore evaluation elements or samples shall be identical in critical constructions to the crystal oscillators to be qualified. When all critical construction and design limits are not able to be represented by a single evaluation element or sample, multiple evaluation elements or samples may be used.

#### 4.7 Screening Test

To supply crystal oscillators in compliance with this specification, certified manufacturer shall perform screening test in accordance with appendix B. Prior to the screening test, production lots shall be re-grouped into inspection lots.

Screening test may be initiated after final sealing process has been completed. Products shall be serialized within each inspection lot prior to screening test to provide traceability between each measurement and product.

| JAXA-QTS-2220 | JAXA                | <b>D</b> | 0.4    |

|---------------|---------------------|----------|--------|

| 18 March 2025 | Parts Specification | Page     | - 21 - |

#### 4.8 Quality Conformance Inspection

Quality conformance inspection shall be performed in accordance with appendix C on inspection lots which passed screening tests. Sampled products shall be disposed of in accordance with paragraph C.3.6. When products to be shipped and qualification test sample are within same inspection lot, qualification test results may be used as quality conformance inspection results for the first article.

#### 4.9 Long-Term Storage

4.9.1 Disposition of Products Stored for a Long Term at Certified manufacturer's Site

When products have been stored at certified manufacturer's site for 24 months or longer

after the quality conformance inspection, certified manufacturer may conduct the

electrical characteristics test (Table C-1) as a retest prior to delivery to the purchaser,

and deliver the products that pass the test. If products fail in any subgroup inspection,

100% inspection shall be performed for items in that subgroup. The crystal oscillators

which are judged acceptable can be delivered as products. Failed products shall be

removed from the lot and shall be declared defective. Paragraph 4.3.4.1 of JAXA-QTS2000 shall also be applicable.

#### 4.9.2 Storage by Purchasers

Conditions and period of storage by purchasers shall be specified in the detail specification, if necessary.

#### 4.10 Change of Tests and Inspections

Any change to the in-process inspection, screening test and quality conformance inspection as specified in this specification shall be in accordance with paragraphs 4.3.5 and A.4.4.2 of JAXA-QTS-2000.

#### 5. PREPARATION FOR DELIVERY

#### 5.1 Packaging

Certified manufacturer shall package the products individually prior to delivery. The package shall have a construction to hold the products securely and protect the products from mechanical shocks. The package shall protect the products from moisture and be free of sharp edges or burrs on the external surfaces. It is desirable that the package allows visual inspection without opening the package. The packaging materials shall not break, peel off, crumble, loosen, accumulate static electricity or corrode. Tapes or adhesives shall not be used to secure the products. Proper protection shall be provided to ESD sensitive products. Individual shipping packages shall be placed in a shipping container to protect the products from possible damages during shipment.

| JAXA-QTS-2220 | JAXA                |      | 00            |

|---------------|---------------------|------|---------------|

| 18 March 2025 | Parts Specification | Page | <b>– 22 –</b> |

#### 5.2 Marking on Package

Each shipping package shall have the markings specified in b) through e) of paragraph 3.4.1. However, when the markings on the products are clearly visible from outside of the shipping package, those markings on the package may be exempted. For packages with ESD protection, a marking "ESD sensitive" shall be added. All markings shall be waterproof.

The marking requirements for each shipping package shall also apply to the shipping container. However, the quantity, applicable specification number, year and month of packaging and inspection results shall be marked additionally except for the marking specified in paragraph 3.4.1d).

#### 6. NOTES

#### 6.1 Definition of Terms

The following definition of terms is used in this specification.

a) Chip:

Circuit elements used in crystal oscillator without a package and leads.

b) Substrate:

The base element on which the element is formed or mounted.

c) Device type:

Refers to a specific configuration of crystal oscillator. For example, products made by different certified manufacturers using different mechanical arrangements and materials are referred to as "the same device type" if those devices are functionally and physically interchangeable at the semiconductor chip or substrate level.

d) Package type:

Refers to a specific package configuration. Packages with the same package configuration, materials (including mounting materials such as bonding wires and semiconductor chips), components and assembly processes are of the same package type.

e) Final seal:

Manufacturing process that do not allow processing related to the internals without disassembling the crystal oscillator.

f) Delta limit:

The maximum value at which a specified parameter is allowed to vary from its pretest measured value as a criteria for acceptance in a specified test.

Note: If represented in percentage, delta limit shall indicate a percentage with respect to a pre-test value.

g) Wafer lot:

A group of wafers processed together in each process.

h) Substrate lot:

A group of substrates formed together in each process.

i) Production lot:

A group of crystal oscillators manufactured (or being manufactured) using the same manufacturing technology, materials, controls, design and production line. When

| JAXA-QTS-2220 | JAXA                | Dogo | 22     |

|---------------|---------------------|------|--------|

| 18 March 2025 | Parts Specification | Page | - 23 - |

multiple device types are manufactured in the same processes up to the final seal process, the production lot may include those device types.

j) Inspection lot:

A group of crystal oscillators with the same package type and lead finish. An inspection lot may include multiple device types. Inspection lots are usually divided into inspection sub-lots.

k) Inspection sub-lot:

A group of single device type crystal oscillators with the same package type and lead finish. Inspection sub-lots are processed together in all manufacturing processes.

I) Thin-film:

Film formed on substrate surface by vacuum deposition, ion sputtering or gas phase reaction, among other methods.

m) Thick-film:

Film formed by baking, among other methods, after ink paste is coated, sprayed or printed on substrate surface.

n) Ferrite core:

Ferrite core is produced by forming and baking materials that are made of several layers of various metal oxide films. The primary ingredient of those metal oxide films is iron oxide. The chemical composition of ferrite core is MOFe<sub>2</sub>O<sub>3</sub> (M indicates metals).

o) Single event characteristics:

Specific characteristics that cause malfunction or permanent damage in circuit elements by the incidence of a single high-energy particle.

p) Design specification:

Document providing qualification coverage for design of crystal oscillator.

q) Procurement specification:

Document prepared by certified manufacturer and applicable to purchase of materials for crystal oscillator manufacturing (refer to paragraph 4.2). This document is included in product assurance documents.

r) First article:

Product delivered at first time for detail specification.

s) Crystal oscillator XO:

A crystal oscillator without temperature control or temperature compensation. The frequency-temperature characteristics of the oscillator depend on the quartz crystal units.

#### 6.2 Notes for Certified manufacturer

#### 6.2.1 Preparation and Registration of Application Data Sheet

Certified manufacturer shall prepare application data sheet in accordance with appendix G of JAXA-QTS-2000 and register it with JAXA.

In the case of products based on purchaser's individual requirements (refer to paragraph 6.3.1), certified manufacturer may be exempt from preparing the application data sheet, when certified manufacturer takes counsel with the purchaser about necessity of the

| JAXA-QTS-2220 | JAXA                | Dens | _ 24 _               |

|---------------|---------------------|------|----------------------|

| 18 March 2025 | Parts Specification | Page | <i>–</i> 24 <i>–</i> |

application data sheet and the exemption is approved by certified manufacturer's TRB (refer to paragraph 3.2.2).

#### 6.3 Notes for Purchaser

#### 6.3.1 Items to be specified at Procurement

To purchase crystal oscillators in accordance with this specification, following items shall be specified:

- a) Part number

- b) This specification number

- c) Detail specification number

- d) Test data to be submitted for the delivery and whether the source inspection is performed or not.

- e) Others

Requirements other than those defined in this specification may be specified for specific applications as item e). However, if the requirements conflict with the existing requirements in this specification, the purchaser shall not request certified manufacturer to indicate that the crystal oscillator complies with this specification.

#### 6.3.2 Review of Application Data Sheet

Application data sheets contain detailed data at the time of qualification of crystal oscillators and contain more detailed information than the detailed specifications, which is required for selection and design tasks. Purchaser shall review the application data sheet prior to procurement.

#### **APPENDIX A**

## REQUIREMENTS FOR SEMICONDUCTOR CHIPS, SUBASSEMBLY AND SEMI-ASSEMBLY CRYSTAL OSCILLATORS

| A.1. Sco | ppeA-                                                                     | -1 |

|----------|---------------------------------------------------------------------------|----|

| A.2. Rec | quirementsA                                                               | -1 |

| A.2.1    | Design and Construction of Semiconductor ChipsA                           | -2 |

| A.2.1.   | 1 Current Density of Metallization                                        | -2 |

| A.2.1.   | 2 GlassivationA                                                           | -2 |

| A.2.1.   | 3 Semiconductor Chip Thickness                                            | -3 |

| A.2.1.   | 4 Plating for Back Surface of Semiconductor ChipA                         | -3 |

| A.2.1.   | 5 Radiation Hardness AssuranceA                                           | -3 |

| A.2.2    | Lot Evaluation Test of Semiconductor ChipsA                               | -3 |

| A.2.2.   | 1 Samples and Sampling MethodsA                                           | -3 |

| A.2.2.   | 2 Failure and RetestA                                                     | -4 |

| A.2.2.   | 3 Lot Evaluation Test RecordsA                                            | -4 |

| A.2.3    | Lot Evaluation Test for MIL, ESA and JAXA Qualified Semiconductor ChipsA- | -4 |

| A.2.3.   | 1 Notice of Procurement                                                   | -5 |

| A.2.4    | Selection and Procurement of Parts such as Passive ElementsA              | -5 |

| A.2.4.   | 1 Capacitor Chips, Resistor Chips and Inductor ChipsA                     | -5 |

| A.2.4.   |                                                                           |    |

| A.2.4.   | 3 Printed Wiring BoardsA                                                  | -6 |

| A.2.4.   |                                                                           |    |

#### APPENDIX A

- A-1 -

### REQUIREMENTS FOR SEMICONDUCTOR CHIPS, SUBASSEMBLY AND SEMI-ASSEMBLY CRYSTAL OSCILLATORS

#### A.1. Scope

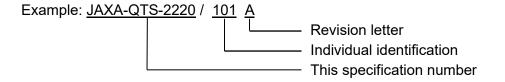

This appendix establishes the requirements for semiconductor chips, subassembly and semi-assembly crystal oscillators. From semiconductor chips acceptance to crystal oscillator assembly is shown in Figure A-1.

Figure A-1: From semiconductor chips acceptance to crystal oscillator assembly

#### A.2. Requirements

Certified manufacturer shall verify quality of semiconductor chips used for crystal oscillators through lot evaluation tests for each lot before the semiconductor chips are used. Specification shall be prepared to establish electrical parameters, test methods, etc.

| JAXA-QTS-2220 | JAXA                | D    | ۸.0     |

|---------------|---------------------|------|---------|

| 18 March 2025 | Parts Specification | Page | – A-2 – |

#### A.2.1 Design and Construction of Semiconductor Chips

Certified manufacturer shall verify that design and construction of semiconductor chips meet the following requirements.

#### A.2.1.1 Current Density of Metallization

Unless otherwise specified, the metallization shall be designed so that, when assumed to be properly built up, the current density through it, under the worst case operating conditions, does not exceed the maximum allowable current densities shown in Table A-1.

Table A-1. Maximum Allowable Current Density of Metallization

| Metallization material                       | Maximum allowable current density (A/cm²) |

|----------------------------------------------|-------------------------------------------|

| Aluminum (99.99% purity or doped)            | 2 x 10⁵                                   |

| High melting point metal (Mo, W, Ti-W, Ti-N) | 5 x 10⁵                                   |

| Gold                                         | 6 x 10⁵                                   |

| All other (unless otherwise specified)       | 2 x 10 <sup>5</sup>                       |

Maximum current densities shall be calculated using current and cross section areas which are determined as follows.

- a) Use a current value equal to the maximum continuous current (at full fan-out for digital or at the maximum load for linear) or equal to the simple time-averaged current obtained at the maximum rated frequency or duty cycle with the maximum load, whichever results in the greater current value. Currents shall be calculated on the assumption that currents flow uniformly through the conductor's cross section driven by the maximum recommended rating voltage.

- b) Use the minimum allowable metallization thickness within the range specified in the manufacturing specification and controls.

- c) Use the minimum actual design metallization widths, not mask widths, including appropriate allowance for narrowing or undercutting experienced in metal etching.

- d) Areas of the barrier metals and nonconductive materials shall not be included in the calculation of the metallization cross section.

- e) Use the cross section obtained from steps b) through d) multiplied by 0.75 for calculation of the maximum current density to compensate for reduction of the metallization cross section due to thinning, bond or scratches.

#### A.2.1.2 Glassivation

Unless otherwise specified in the detail specification, all semiconductor chips shall be glassivated. The glassivation thickness shall be a minimum of  $0.40\mu m$  for  $SiO_2$  or a

| JAXA-QTS-2220 | JAXA                | Dawa | A 2     |

|---------------|---------------------|------|---------|

| 18 March 2025 | Parts Specification | Page | – A-3 – |

minimum of  $0.20\mu m$  for  $Si_3N_4$  unless otherwise specified in the detail specification. The glassivation shall cover all conductor surfaces except for bonding pads.

#### A.2.1.3 Semiconductor Chip Thickness

Unless otherwise specified in detail specification, the minimum semiconductor chip thickness shall be 0.15mm.

#### A.2.1.4 Plating for Back Surface of Semiconductor Chip

When the back surface of semiconductor chip is plated with gold, the thickness shall be between  $0.10\mu m$  and  $1.00\mu m$ . Electrolytic plating shall not be used for gold plating on the back surface of semiconductor chips.

#### A.2.1.5 Radiation Hardness Assurance

Semiconductor chips used for radiation hardened crystal oscillators shall pass the lot evaluation tests of subgroup 4 in Tables A-2 to A-4.

When total dose test has been performed on the same lot of semiconductor chips used, the test data may be used. Single event test results shall be evaluated on a semiconductor chip basis in accordance with appendix A. When test data on semiconductor chips of the same design is available, the test data may be used.

#### A.2.2 Lot Evaluation Test of Semiconductor Chips

Certified manufacturer shall verify for each wafer lot that the semiconductor chips pass the lot evaluation tests specified in Tables A-2 to A-4. Unless otherwise specified in the detail specification, Table A-2 shall be applied for lot evaluation test. Table A-3 or Table A-4, which performs some tests as in-process tests of crystal oscillators, may be applied when semiconductor chips are mounted such that they can be characterized as separate chips. In this case, tests specified in Table A-3 shall be performed for subassembly parts. Tests specified in Table A-4 shall be performed for semi-assembly products of crystal oscillators. Paragraph A.2.3 may apply to MIL, ESA and JAXA qualified semiconductor chips.

Certified manufacturer may modify or optimize the content of this evaluation test by clarifying the basis on which the quality assurance requirements are met in accordance with paragraph 4.3.5 of JAXA-QTS-2000.

#### A.2.2.1 Samples and Sampling Methods

- Samples for the lot evaluation test shall be as follows.

Samples shall be randomly selected from semiconductor chips produced from the single wafer lot.

- b) Samples for the subgroups 2c) and 2d) shall be prepared using the same materials and techniques of semiconductor mounting and wire bonding as those used in the crystal oscillator.

| JAXA-QTS-2220 | JAXA                |      |         |

|---------------|---------------------|------|---------|

| 18 March 2025 | Parts Specification | Page | – A-4 – |

c) Unless otherwise specified in detail specification, samples for the subgroups 3, 4a) and 5 of Table A-2, subgroups 3, 4a) and 5 of Table A-3 and subgroups 4a) and 5 of Table A-4 shall be packaged and sealed in compliance with paragraph 3.3.8 (except for the requirement specified in paragraph 3.3.8 c)).

#### A.2.2.2 Failure and Retest

If lot evaluation test failed because of an equipment failure or an operator error, the cause and problem shall be documented in detail and the failed chips may be replaced with chips made from the same wafer. The replaced chips shall pass all tests performed previously with the failed chips. The remaining tests shall then be performed.

#### A.2.2.3 Lot Evaluation Test Records

Records of lot evaluation tests shall contain a minimum of the following items and shall be managed in accordance with quality assurance program requirements specified in paragraph 3.2.1.

- a) Test items

- b) Document number and issue date of test methods

- c) Quantity of passed and failed chips

- d) Date of test and name or identification code of the operator

- e) Records accompanying the tests (e.g., temperature charts)

- f) Quantitative data including electrical parameter tests

#### A.2.3 Lot Evaluation Test for MIL, ESA and JAXA Qualified Semiconductor Chips

When certified manufacturer procures the semiconductor chips corresponding to a) or b) specified below in accordance with paragraph C.3.3, appendix C of MIL-PRF-38534, ESCC 5000 or ESCC 9000 qualified products c) and JAXA qualified products d) or e), subgroups 2b) Inspection for external dimensions (semiconductor chips), d) Die shear strength test, 4a) Radiation hardness test <sup>(1)</sup> and 5a) Electrostatic discharge sensitivity test <sup>(1)</sup> of Table A-2 shall be performed as lot evaluation test.

The test shall be performed as specified in paragraphs A.2.2.1, A.2.2.2 and A.2.2.3.

When total dose test has been performed on the same lot of semiconductor chips used, the test data may be used. Single event test results shall be evaluated on a chip-by-chip basis in accordance with appendix A. When test data on the same lot of semiconductor chips of the same design are available, they may be used.

- a) JANKC chips qualified by MIL-PRF-19500 (listed on QML-19500) or Class V chips qualified by MIL-PRF-38535 (listed on QML-38535).

- b) Chips other than JANKC products qualified by MIL-PRF-19500 (listed on QML-19500) and class V chips qualified by MIL-PRF-38535 (listed on QML-38535),

| JAXA-QTS-2220 | JAXA                |      | A 5     |

|---------------|---------------------|------|---------|

| 18 March 2025 | Parts Specification | Page | – A-5 – |

which are semiconductor chips that have been evaluated and passed in accordance with TABLE C-II for Class K, appendix C of MIL-PRF-38534.

- c) ESCC 5000 or ESCC 9000 qualified Level 1 chip

- d) JAXA-QTS-2010 qualified chip

- e) JAXA-QTS-2030 qualified chip

Note: <sup>(1)</sup> The radiation hardness test and/or electrostatic discharge sensitivity test may be exempted when the semiconductor chips listed on QML-19500 or QML-38535, ESCC 5000 or ESCC 9000 qualified chips and JAXA-QTS-2010 or JAXA-QTS-2030 qualified chips meet the requirements for crystal oscillator.

#### A.2.3.1 Notice of Procurement

The following items shall be specified in procurement specification for purchase of semiconductor chips.

- a) Designation of radiation hardness test and electrostatic discharge sensitivity test (if required by the application of crystal oscillator).

- b) At least the following data as a record:

- 1) Certificate of compliance

- 2) Test results indicating the conformance to a) to e) of paragraph A.2.3, and/or results of lot evaluation (figures and/or measurements)