# INTEGRATED CIRCUITS, Multi-Core Processor, SOI-SOC, CMOS, MONOLITHIC SILICON, HIGH RELIABILITY, SPACE USE,

**DETAIL SPECIFICATION FOR**

Prepared and Established by Mitsubishi Heavy Industries, Ltd.

Issued by Japan Aerospace Exploration Agency

This document is the English version of JAXA QTS/ADS which was originally written and authorized in Japanese and carefully translated into English for international users. If any question arises as to the context or detailed description, it is strongly recommended to verify against the latest official Japanese version.

The release date of the English version of this specification: 24 December 2025

| JAXA-QTS-2010/201 | JAXA                | Done |  |

|-------------------|---------------------|------|--|

| 28 July 2025      | Parts Specification | Page |  |

# Record of Revisions

| Revision | Date         | Description                                                                                         |

|----------|--------------|-----------------------------------------------------------------------------------------------------|

| NC       | 28 July 2025 | Original issued in accordance with VET25310 Revision NC issued by Mitsubishi Heavy Industries, Ltd. |

|          |              | The remainder of this page is intentionally left blank.                                             |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

|          |              |                                                                                                     |

| JAXA-QTS-2010/201 | JAXA                | Dogo | – ii – |

|-------------------|---------------------|------|--------|

| 28 July 2025      | Parts Specification | Page | - 11 - |

# Revision History

| Revision | Date         | Description                                             |

|----------|--------------|---------------------------------------------------------|

| NC       | 28 July 2025 | Original                                                |

|          |              | The remainder of this page is intentionally left blank. |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

|          |              |                                                         |

# J A X A Parts Specification

Page

– iii –

# VET25310

# Contents

| 1. |       |       | <b>\L</b>                                                                   |    |

|----|-------|-------|-----------------------------------------------------------------------------|----|

|    | 1.1   |       | pe                                                                          |    |

|    | 1.2   |       | Number                                                                      |    |

|    | 1.2.  | -     | Individual Identification                                                   |    |

|    | 1.2.2 | _     | Device Type                                                                 |    |

|    | 1.2.3 | _     | Package Configuration                                                       |    |

|    | 1.2.4 |       | Pin Material                                                                |    |

|    | 1.2.  | _     | Radiation Hardness                                                          |    |

|    |       |       | olute Maximum Ratings                                                       |    |

|    | 1.4   |       | ommended Operating Conditions                                               |    |

|    | 1.5   |       | ction and Performance                                                       |    |

|    |       |       | D DOCUMENTS                                                                 |    |

|    | 2.1   |       | licable Documents                                                           |    |

|    | 2.2   |       | er of Precedence                                                            |    |

|    |       |       | EMENTS                                                                      |    |

|    | 3.1   | Des   | ign and Construction                                                        |    |

|    | 3.1.  | 1     | Operating Temperature                                                       |    |

|    | 3.1.2 | 2     | Package Configuration                                                       |    |

|    | 3.1.3 | 3     | Pin Material                                                                |    |

|    | 3.1.4 | 4     | Block Diagram and Pin-Outs                                                  | 11 |

|    | 3.1.  | 5     | Electrical Characteristics                                                  | 11 |

|    | 3.2   | Mar   | king                                                                        | 11 |

|    | 3.3   | Cert  | ification                                                                   | 11 |

|    | 3.4   |       | llity Assurance Program                                                     |    |

| 4. | QUA   | \LIT\ | Y ASSURANCE PROVISIONS                                                      | 12 |

|    | 4.1   | Gen   | eral Requirements                                                           | 12 |

|    | 4.2   | Fun   | ctional Drawing Control                                                     | 12 |

|    | 4.3   | Inco  | ming Materials Control                                                      | 12 |

|    | 4.4   | Man   | ufacturing Process Control                                                  | 12 |

|    | 4.5   | In-P  | rocess Inspection                                                           | 12 |

|    | 4.6   | Scre  | eening                                                                      | 12 |

|    | 4.6.  | 1     | Screening Items and Conditions                                              | 12 |

|    | 4.6.2 | 2     | Electrical Parameters to be Measured                                        | 12 |

|    | 4.6.3 | 3     | Burn-In Test Circuit                                                        | 13 |

|    | 4.6.4 | 4     | Delta Limits                                                                | 13 |

|    | 4.7   | Qua   | lification Test for JAXA-developed Parts and Quality Conformance Inspection | 13 |

|    | 4.7.  | 1     | Test/Inspection Items and Conditions                                        | 13 |

|    | 4.7.2 | 2     | Electrical Parameters to be Measured                                        | 13 |

|    | 4.7.3 | 3     | Exemption of Tests and Inspections                                          | 14 |

|    | 4.8   | Long  | g-Term Storage                                                              | 14 |

|    | 4.8.  | 1     | Disposition of Products Stored for a Long-Term at the Manufacturer's Site   | 14 |

|    | 4.8.2 | 2     | Storage by Purchasers                                                       | 14 |

|    | 4.9   | Cha   | nge of Tests and Inspections                                                | 14 |

|    |       |       |                                                                             |    |

| J                           | AXA-QTS-2010/201                                  | QTS-2010/201 J A X A |      | _ iv _   |

|-----------------------------|---------------------------------------------------|----------------------|------|----------|

|                             | 28 July 2025                                      | Parts Specification  | Page | - IV -   |

|                             |                                                   |                      |      | VET25310 |

| 4                           | .9.1 Inspection of Wat                            | er Lot               |      | 14       |

| 4                           | .9.2 Screening                                    |                      |      | 15       |

| 4                           | 4.9.3 Qualification Test for JAXA-developed Parts |                      | 16   |          |

| -                           | 9.4 Quality Conformance Inspection                |                      |      |          |

| 5. PREPARATION FOR DELIVERY |                                                   |                      | 18   |          |

| 6. N                        | OTES                                              |                      |      | 18       |

| 6.1                         | 6.1 Definition of Terms                           |                      | 18   |          |

| 6.2                         | 6.2 Application Datasheet                         |                      | 18   |          |

| 6.3 Notes for Purchasers    |                                                   | 19                   |      |          |

|                             |                                                   |                      |      |          |

| JAXA-QTS-2010/201 | JAXA                | Dogo | 1   |

|-------------------|---------------------|------|-----|

| 28 July 2025      | Parts Specification | Page | -1- |

# INTEGRATED CIRCUITS, MULTI-CORE PROCESSOR, SOI-SOC, CMOS, MONOLITHIC SILICON, HIGH RELIABILITY, SPACE USE, DETAIL SPECIFICATION FOR

#### 1. GENERAL

### 1.1 Scope

This specification establishes the detail requirements for the monolithic silicon, CMOS, SOI-SOC, Multi-Core Processor (hereinafter referred to as "IC") to be used for electronic equipment installed on spacecrafts such as satellites. Additional requirements specific to a given application may be documented separately (refer to paragraph 6).

The ICs shall be manufactured using the COT method (refer to paragraph 6.1 of JAXA-QTS-2010 Revision D for definition of terms).

#### 1.2 Part Number

The part numbers for the IC covered by this specification are assigned as follows:

| JAXA(1) <u>2010</u> / | <u>201</u>        | <u>01</u>         | <u>X</u>         | <u>Z</u>            | <u>R</u>          |

|-----------------------|-------------------|-------------------|------------------|---------------------|-------------------|

|                       | Individual        | Device            | Package          | Lead                | Radiation         |

|                       | identification    | type              | configuration    | material and finish | hardness          |

|                       | (paragraph 1.2.1) | (paragraph 1.2.2) | (paragraph 1.2.3 | ) (paragraph 1.2.4) | (paragraph 1.2.5) |

#### Notes:

(1) "JAXA" indicates that the part is for space use and may be abbreviated "J."

#### 1.2.1 Individual Identification

The individual identification for the IC shall be the document number of this detail specification.

# 1.2.2 Device Type

The device type defined in this specification shall be as follows:

| <u>Device type</u> | <u>Circuit</u>       |

|--------------------|----------------------|

| 01                 | Multi-Core Processor |

# 1.2.3 Package Configuration

Package configuration of the ICs defined in this specification shall be as follows:

| Package configuration symbol | Package configuration |

|------------------------------|-----------------------|

| X                            | 572 pins, CBGA        |

| JAXA-QTS-2010/201<br>28 July 2025 | J A X A<br>Parts Specification | Page | <b>-2-</b> |

|-----------------------------------|--------------------------------|------|------------|

|-----------------------------------|--------------------------------|------|------------|

## 1.2.4 Pin Material

The pin material of the ICs defined in this specification shall be as shown below. The details shall be as specified in paragraph 3.1.3.

| Finish letter | <u>Pin material</u>                                         |

|---------------|-------------------------------------------------------------|

| Z             | Sn10/Pb90 (center 8x8 terminal, solder balls),              |

|               | Sn63/Pb37 (all terminals except center 8x8 terminal, solder |

|               | balls)                                                      |

#### 1.2.5 Radiation Hardness

# 1.2.5.1 TID Hardness

The radiation hardness (TID hardness) defined in this specification shall be as follows.

<u>Radiation hardness assurance level</u> R 1000 Gy(Si) {1 x 10<sup>5</sup>rad(Si)}

# 1.3 Absolute Maximum Ratings

The absolute maximum ratings common to the ICs defined in this specification shall be as follows.

**Table 1. Absolute Maximum Ratings**

| Item                |                  | Symbol               | Min. | Max.                   | Unit |

|---------------------|------------------|----------------------|------|------------------------|------|

| B                   |                  | Vccq                 | -0.3 | 4.6                    | V    |

| Power supp          | ly voltage       | $V_{DD}$             | -0.3 | 1.4                    | V    |

| Input voltag        | e <sup>(1)</sup> | V <sub>in</sub>      | -0.3 | V <sub>CCQ</sub> + 0.3 | V    |

| Output voltage (1)  |                  | Vo                   | -0.3 | V <sub>CCQ</sub> + 0.3 | V    |

| Output 8mA buffer   |                  | I <sub>O(8mA)</sub>  | -90  | 86                     | mA   |

| current 24mA buffer |                  | I <sub>O(24mA)</sub> | -266 | 267                    | mA   |

| Storage temperature |                  | T <sub>stg</sub>     | -55  | +150                   | °C   |

| Junction ten        | nperature        | Tj                   | -40  | +125                   | °C   |

Note: (1) Shall not exceed +4.6V.

# 1.4 Recommended Operating Conditions

The recommended operating conditions common to the ICs defined in this specification shall be as shown in Table 2.

– 3 –

VET25310

Table 2. Recommended Operating Conditions

| Item                                |                                      | Symbol              | Min.                   | Тур. | Max.                   | Unit |

|-------------------------------------|--------------------------------------|---------------------|------------------------|------|------------------------|------|

| Dower aupply w                      | er supply voltage range              |                     | 3.0                    | 3.3  | 3.6                    | V    |

| Fower supply w                      | ollage range                         | $V_{DD}$            | 1.11                   | 1.2  | 1.29                   | V    |

| High level input                    | voltage                              | V <sub>IH</sub>     | 0.7 x V <sub>CCQ</sub> | -    | V <sub>CCQ</sub> + 0.3 | V    |

| Low level input voltage             |                                      | VIL                 | -0.3                   | -    | 0.2 x Vccq             | V    |

| Operating board surface temperature |                                      | T <sub>b</sub> (1)  | -37 <sup>(5)</sup>     | -    | +120                   | °C   |

| Operating junction temperature      |                                      | T <sub>j</sub> (2)  | -40 <sup>(6)</sup>     | -    | +125                   | °C   |

| When the PLL on the chip is used    |                                      | f                   | -                      | 20   | -                      | MHz  |

| frequency                           | When the PLL on the chip is not used | f <sub>extclk</sub> | -                      | 100  | -                      | MHz  |

#### Notes:

- (1) Defined as the temperature at the board surface (directly beneath the chip edge).

- (2) T<sub>J</sub> is calculated as follows.

$T_J = T_b + \theta_{j-b} \times P_D$

Where,

T<sub>b</sub>: Operating board surface temperature (°C)

θ<sub>i-b</sub>: Standard thermal resistance between the junction and board (1.8°C/W) (3)

P<sub>D</sub>: Power dissipation (1.8W)<sup>(4)</sup>

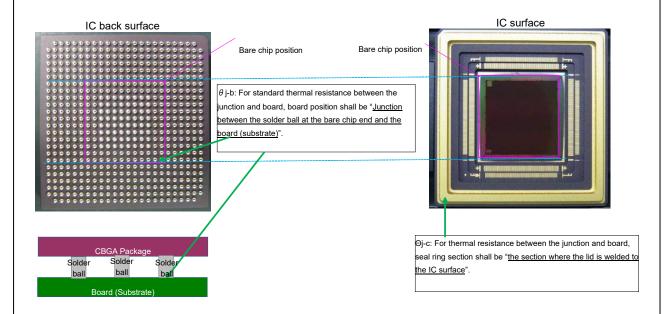

(3) Defined as the thermal resistance calculated in the simulation between "the junction and board surface (directly beneath the chip edge)". For reference, the thermal resistance  $\Theta_{j-c}$  calculated in the simulation between "the junction and case (seal ring section)" is  $7.1^{\circ}$ C/W. Thermal design shall be performed to ensure that the absolute maximum rating  $T_{jmax}$  is not exceeded. The locations of  $\theta_{j-b}$  and  $\Theta_{j-c}$  are shown below.

- $^{(4)}$  Simulation results under the worst-case power consumption conditions (manufacturing process: fast corner, temperature: 125°C,  $V_{DD}$ : 1.29V,  $V_{CCQ}$ : 3.6V, toggle rate: 10%, operation frequency: 160MHz, including I/O power consumption).

- (5) Specified as the upper limit value for the test conditions of the package.

- (6) Specified as the upper limit value for the test conditions of the wafer.

| 20 July 2025 Faits Specification | JAXA-QTS-2010/201<br>28 July 2025 | J A X A<br>Parts Specification | Page | -4- |

|----------------------------------|-----------------------------------|--------------------------------|------|-----|

|----------------------------------|-----------------------------------|--------------------------------|------|-----|

# 1.5 Function and Performance

The function and performance of the ICs defined in this specification shall be as shown in Table 3

Table 3. Function and Performance (1/4)

| Item                         | Specification                                       | Construction           | Overview                                                                                                                                                                                                                                                                                              |

|------------------------------|-----------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor core               | Renesas RXv3                                        | 2 cores                | <ul> <li>Operation frequency: 160MHz         (Temperature: +125°C, operation voltage: 1.11V, worst path)</li> <li>Operation frequency: 190MHz         (Temperature:+25°C, operation voltage: 1.2V, worst path)</li> <li>Double-precision FPU support (customized for Multi-Core Processor)</li> </ul> |

| Core peripheral functions    | DMAC<br>(DMA controller)                            | CPU0: 4ch<br>CPU1: 4ch | - Equivalent to RX64M product (DMACAa) by Renesas                                                                                                                                                                                                                                                     |

|                              | DTC<br>(Data transfer controller)                   | CPU0: 1ch<br>CPU1: 1ch | - Equivalent to RX64M product (DTCa) by Renesas                                                                                                                                                                                                                                                       |

|                              | EXDMAC (EXDMA controller)                           | CPU0: 2ch<br>CPU1: -   | - Equivalent to RX64M product (EXDMACa) by Renesas - External bus transfer only - However, the following functions are excluded: (1) Transfer to SDRAM (2) Control via external pins (EDREQ and EDACK)                                                                                                |

|                              | BSC<br>(Bus controller)                             | CPU0: 1ch<br>CPU1: -   | - Equivalent to RX64M product (BSC) by Renesas                                                                                                                                                                                                                                                        |

|                              | ICU<br>(Interrupt controller)                       | CPU0: 1ch<br>CPU1: -   | - Equivalent to RX64M product (ICUA) by Renesas                                                                                                                                                                                                                                                       |

| High-speed communication I/F | SpaceWire<br>(SpaceWire<br>communication function)  | CPU0/1 shared:<br>6ch  | - Refer to Table 4 Support for SpaceWire/RAMP, SpaceWire-PTP and RAW packet                                                                                                                                                                                                                           |

|                              | Ethernet<br>(EthernetAVB<br>communication function) | CPU0/1 shared:<br>2ch  | - Refer to Table 4.                                                                                                                                                                                                                                                                                   |

J A X A Parts Specification

Page

-5-

VET25310

# Table 3. Function and Performance (2/4)

| Item                        | Specification                           | Construction                     | Overview                                                             |  |

|-----------------------------|-----------------------------------------|----------------------------------|----------------------------------------------------------------------|--|

| Low-speed communication I/F |                                         |                                  | - Refer to Table 4.                                                  |  |

|                             | CAN<br>(CAN communication<br>function)  | CPU0: 1ch<br>CPU1: 1ch           | - Refer to Table 4.                                                  |  |

|                             | Multifunction serial (SCI)              | CPU0: Max. 2ch<br>CPU1: Max. 2ch | - Refer to Table 4.<br>- Shared pins with GPIO                       |  |

|                             | SPI<br>(SPI communication<br>function)  | CPU0: Max. 1ch<br>CPU1: Max. 1ch | - Refer to Table 4.<br>- Shared pins with GPIO                       |  |

|                             | I2C<br>(I2C communication<br>function)  | CPU0: Max. 1ch<br>CPU1: Max. 1ch | - Refer to Table 4.<br>- Shared pins with GPIO                       |  |

| Universal I/O               | GPIO<br>(Universal input and<br>output) | CPU0/1 shared:<br>Max. 76ch      | - Refer to Table 4 Shared pins with PWM, SPI, I2C, SCI, TMR and CMTW |  |

|                             | PWM (GPT)<br>(Universal PWM timer)      | CPU0: Max. 4ch<br>CPU1: Max. 4ch | - Refer to Table 4.<br>- Shared pins with GPIO                       |  |

| Timer                       | TMR<br>(8-bit timer)                    | CPU0: Max. 1ch<br>CPU1: Max. 1ch | - Refer to Table 4.<br>- Shared pins with GPIO                       |  |

|                             | WDTA<br>(Watchdog timer)                | CPU0: 1ch<br>CPU1: 1ch           | - Refer to Table 4.                                                  |  |

| Processing support          | CRC (CRC processing circuit)            | CPU0: 1ch<br>CPU1: 1ch           | - Refer to Table 4.                                                  |  |

|                             | DOC<br>(Data processing circuit)        | CPU0: 1ch<br>CPU1: 1ch           | - Refer to Table 4.                                                  |  |

| Internal memory             | Code RAM                                | CPU0/1 shared:<br>4MByte         | - Implemented accelerator and memory scrubber                        |  |

|                             | Shared memory                           | CPU0/1 shared:<br>2MByte         | - Implemented accelerator and memory scrubber                        |  |

|                             | Local RAM                               | CPU0: 64kByte<br>CPU1: 64kByte   | - Implemented memory scrubber (option)                               |  |

J A X A Parts Specification

Page

-6-

VET25310

# Table 3. Function and Performance (3/4)

| Item            | Specification                     | Construction           | Overview                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|-----------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

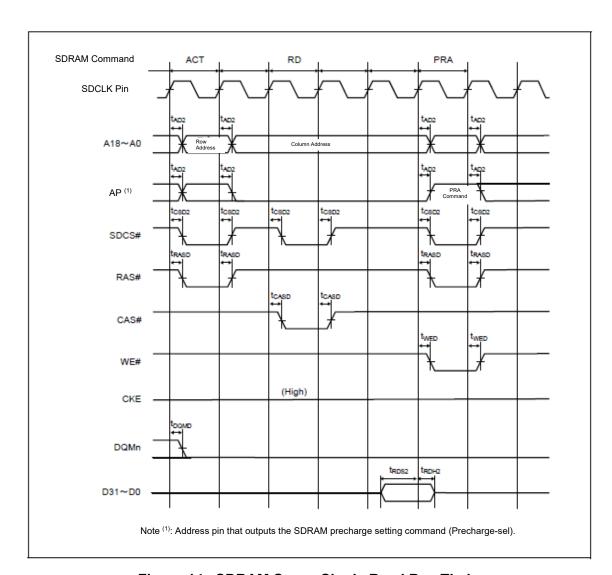

| External memory | Universal external bus controller | CPU0: 1ch<br>CPU1: -   | - Equivalent to RX64M product (CSC) by Renesas                                                                                                                                                                                                                                                                                                                     |

|                 | SDRAM controller                  | CPU0: 1ch<br>CPU1: -   | - RX64M product (SDRAMC) by Renesas with the following modifications.  (1) Added error correction functions (capable of correcting multi-bit errors using Reed-Solomon codes). Note that the function may be enabled or disabled.  (2) Expanded the address space to a maximum of 512MB.  - Throughput between external SDRAM and internal memory: Minimum 100Mbps |

| Debug I/F       |                                   |                        | - Compatible with Renesas original emulators (E1 emulator).                                                                                                                                                                                                                                                                                                        |

| Boot function   |                                   |                        | <ul> <li>After reset, CPU0 acquires the fixed address of the CS1 area as a vector and executes the program.</li> <li>The following addresses may be switched by configuring the MODE pin (external terminal).</li> <li>(1) CS1 base address</li> <li>(2) 2Mbyte offset</li> <li>(3) 4Mbyte offset</li> </ul>                                                       |

| Security        |                                   | CPU0: 1ch<br>CPU1: 1ch | <ul> <li>Implemented the functions shown in Table 5.</li> <li>Supports the equivalent of TSL 1.3 authentication methods.</li> </ul>                                                                                                                                                                                                                                |

Page

**-7-**

VET25310

# Table 3. Function and Performance (4/4)

| Item              | Specification                           | Construction               | Overview                                                                                                                                                                                                                                                                                                   |

|-------------------|-----------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power consumption | Maximum 1W                              | -                          | <ul> <li>Temperature: +25°C, operation voltage: 1.2V, except for external I/O power consumption.</li> <li>Total power consumption of Multi-Core Processor (when using 2 cores).</li> </ul>                                                                                                                 |

|                   | 1.8W<br>(Worst case) (For<br>reference) | -                          | - Simulation results under worst-case power consumption conditions (manufacturing process: fast corner, temperature: +125°C, VDD: 1.29V, VCCQ: 3.6V, toggle rate: 10%, operating frequency: 160MHz, including I/O power consumption) Total power consumption of Multi-Core Processor (when using 2 cores). |

| Radiation         | TID hardness                            | -                          | - 100krad(Si)                                                                                                                                                                                                                                                                                              |

| hardness          | SEL hardness                            | -                          | - Minimum threshold LET:<br>75 MeV/(mg/cm²)<br>(Tj = +125°C)                                                                                                                                                                                                                                               |

|                   | SEU hardness                            | Logic cell<br>(Flip-Flop)  | - Minimum threshold LET: 40 MeV/(mg/cm²)  - Maximum saturated cross section (Flip-Flop): 2 x 10-9 (cm²/cell)                                                                                                                                                                                               |

|                   |                                         | Local RAM                  | - Minimum threshold LET: 40 MeV/(mg/cm²) (2) (3)  - Maximum saturated cross section: 2 x 10-9 (cm²/bit)                                                                                                                                                                                                    |

|                   |                                         | Code RAM and shared memory | Based on the saturated cross section (9.96x10 <sup>-10</sup> (cm²/bit)), the Scrubbing Period <sup>(4)</sup> was calculated from the target threshold LET for each orbit.     The target threshold LET for each orbit and Scrubbing Period are shown in <sup>(5)</sup> .                                   |

#### Notes:

- (1) This area may be used for program storage. However, an accelerator for external memory access has not been implemented.

- (2) The LET value when the saturated cross section is 1/100th of the saturated cross section without SEU countermeasure.

- (3) The LET value without scrubbing. The ICs have EDAC and scrubbing functions.

- (4) The Scrubbing Period is defined as the amount of time required to read, modify and write all memory within the specified range.

(5) Refer to the following table.

| No. | Target LET Threshold <sup>(6)</sup> for Each Orbit               | Scrubbing Period |

|-----|------------------------------------------------------------------|------------------|

| 1   | Equivalent to a threshold LET ≥ 25 MeV/(mg/cm²) in the ISS orbit | 327680 (seconds) |

| 2   | Equivalent to a threshold LET ≥ 40 MeV/(mg/cm²) in the GEO orbit | 1310 (seconds)   |

- (6) Defined as the results of calculating the threshold LET (the LET value when the saturated cross section is 1/100th of the saturated cross section without SEU countermeasure) using the saturated cross section.

- (7) The calculation conditions for orbital flux when calculating the Scrubbing Period are shown below.

- Aluminum shielding thickness: 2.54mm

- Solar activity: Solar min.

Page

-8-

VET25310

# Table 4. List of Peripheral IP Addresses (1/2)

| IP name                    | Overview                             | СР               | J0   | СР               | U1   | ID Specification                                                                                                               |

|----------------------------|--------------------------------------|------------------|------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------|

| ir name                    | Overview                             | unit             | ch   | unit             | ch   | IP Specification                                                                                                               |

| SpW Engine                 | SpaceWire communication function     | 6                | 6    | Share<br>CP      |      |                                                                                                                                |

| SpW Router                 | SpaceWire Router                     | 2                | 6    | Share<br>CP      |      |                                                                                                                                |

| Mil-STD-1553B              | MIL-STD-1553B communication function | 2                | 2    | Share<br>CP      |      |                                                                                                                                |

| GPIO                       | Universal input and output           | 1                | 76   | Share<br>CP      |      |                                                                                                                                |

| Ethernet (for DualUse)     | EthernetAVB communication function   | 2                | 2    | Share<br>CP      |      | - Equivalent to RZA1H<br>(EthernetAVB) by<br>Renesas                                                                           |

| PWM (GPT)                  | Universal PWM timer                  | 1                | 4    | 1                | 4    | - Equivalent to RX64M<br>product (GPTa) by<br>Renesas                                                                          |

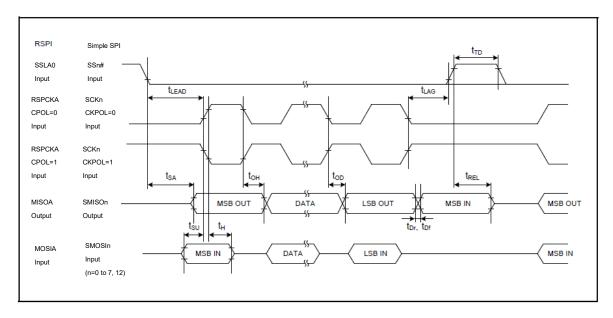

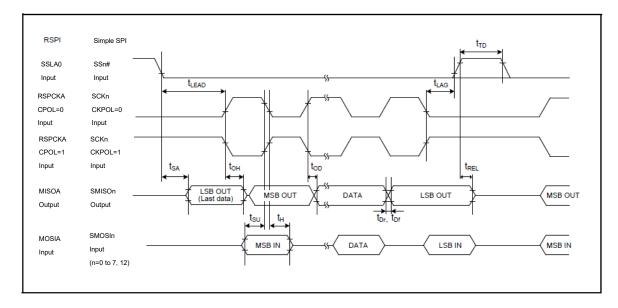

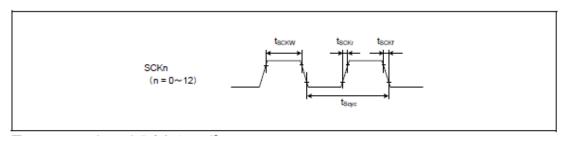

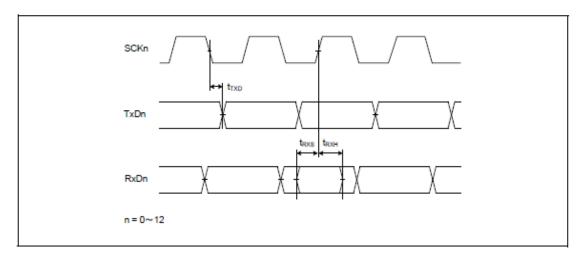

| SPI                        | SPI communication function           | 1                | 1    | 1                | 1    | - Eqivalent to RX64M<br>product (RSPIa) by<br>Renesas                                                                          |

| Multifunction serial (SCI) | Serial communication function        | 2                | 2    | 2                | 2    | - Equivalent to RX64M<br>product (SCIg) by<br>Renesas                                                                          |

| CRC                        | CRC processing unit                  | 1                | 1    | 1                | 1    | - Equivalent to RX64M<br>product (CRC) by<br>Renesas                                                                           |

| DOC                        | Data processing unit                 | 1                | 1    | 1                | 1    | - Eqivalent to RX64M<br>product (DOC) by<br>Renesas                                                                            |

| WDTA                       | Watchdog timer                       | 1                | 1    | 1                | 1    | - Eqivalent to RX64M<br>product (WDTA) by<br>Renesas                                                                           |

| OS timer                   | 16/32 bit compare match timer        | 5 <sup>(1)</sup> | 5(1) | 5 <sup>(1)</sup> | 5(1) | - Equivalent to RX64M<br>product (CMTW) by<br>Renesas<br>Note <sup>(1)</sup> : Two of the five<br>channels share<br>CPU0/CPU1. |

| CMTW                       | 16/32 bit compare match timer        | 2                | 2    | 2                | 2    | - Equivalent to RX64M<br>product (CMTW) by<br>Renesas                                                                          |

| TMR                        | 8bit timer                           | 1                | 1    | 1                | 1    | - Equivalent to RX64M<br>product (TMR) by<br>Renesas                                                                           |

| JAXA-QTS-2010/201 | JAXA                | Dana | 0                   |

|-------------------|---------------------|------|---------------------|

| 28 July 2025      | Parts Specification | Page | <b>–</b> 9 <b>–</b> |

# Table 4. List of Peripheral IP Addresses (2/2)

| ID name   | Overview                   | CPI  | J0 | СР   | U1 | ID Consideration                                       |

|-----------|----------------------------|------|----|------|----|--------------------------------------------------------|

| IP name   | Overview                   | unit | ch | unit | ch | IP Specification                                       |

| CAN       | CAN communication function | 1    | 1  | 1    | 1  | - Equivalent to RX64M<br>product (CAN) by<br>Renesas   |

| I2C(RIIC) | I2C communication function | 1    | 1  | 1    | 1  | - Equivalent to RX64M<br>product (RIICa) by<br>Renesas |

| CPG       | Clock generation circuit   | 1    | 1  | -    | -  |                                                        |

# Table 5. Security Function and Cryptographic Performance

| Major Function Item                             | Minor Function Item                           | Function Summary                                                                                  |  |  |  |

|-------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| Encryption and decryption function              | Data encryption function                      | Function for encrypting data and generating signature and authentication codes                    |  |  |  |

|                                                 | Encrypted<br>communication<br>function        | Function for keeping the contents of communication data confidential from third parties           |  |  |  |

|                                                 | Classified information management function    | Function for restricting access to confidential information                                       |  |  |  |

| Falsification prevention and detection function | Destination authentication function           | Function for inhibiting communication with unknown parties                                        |  |  |  |

|                                                 | Software authentication function              | Function for inhibiting the operation of unauthorized software                                    |  |  |  |

|                                                 | Countermeasures for flaw exploitation attacks | Function for preventing leakage of confidential information due to out of specification operation |  |  |  |

|                                                 | Cryptographic Performance                     |                                                                                                   |  |  |  |

|                                                 | Security level indicate                       | or: 128-bit security                                                                              |  |  |  |

| JAXA-QTS-2010/201<br>28 July 2025 | J A X A<br>Parts Specification | Page | - 10 - |

|-----------------------------------|--------------------------------|------|--------|

|-----------------------------------|--------------------------------|------|--------|

#### 2. RELATED DOCUMENTS

# 2.1 Applicable Documents

The documents listed below shall form a part of this specification to the extent specified herein.

| a) | JAXA-QTS-2010D | Integrated Circuits, High Reliability, Space Use, General    |

|----|----------------|--------------------------------------------------------------|

|    |                | Specification for                                            |

| b) | MIL-STD-883L   | Test Methods Standards – Microcircuits                       |

| c) | JAXA-QTS-2000F | Common Parts/Materials, Space Use, General Specification     |

|    |                | for                                                          |

| d) | JESD22-B115A   | SOLDER BALL PULL                                             |

| e) | CCA-115025A    | Proceedings of lot certification                             |

| f) | JERG-0-043E    | Standard for Surface Mount Soldering Process for Space Use   |

| g) | JERG-0-054A    | Standard for BGA/CGA Mounting Process for Space Use          |

| h) | J-STD-002E     | Solderability Tests for Component Leads, Terminations, Lugs, |

|    |                | Terminals and Wires                                          |

## 2.2 Order of Precedence

Order of precedence shall be as specified in paragraph G.2.3, Appendix G of JAXA-QTS-2010.

## 3. REQUIREMENTS

To supply the ICs under this specification, certified manufacturers shall comply with all requirements specified in this section and paragraph G.3, Appendix G of JAXA-QTS-2010.

## 3.1 Design and Construction

Design and construction of the ICs shall be in accordance with the requirements specified in this section and paragraph G.3.3, Appendix G of JAXA-QTS-2010.

# 3.1.1 Operating Temperature

The operation temperature range of the ICs shall be defined as the board surface (directly beneath the chip edge) temperature. The minimum and maximum operating temperatures shall be -37°C and +120°C, respectively.

# 3.1.2 Package Configuration

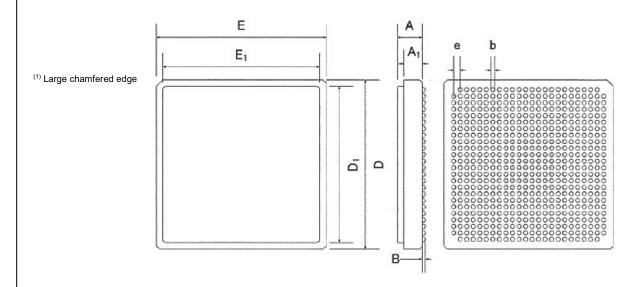

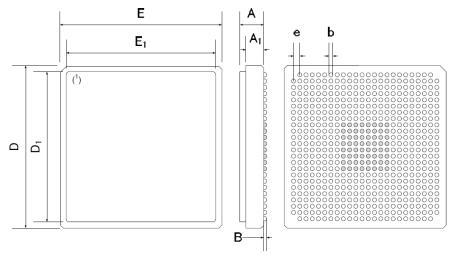

The package configuration (including mass) shall meet the requirements specified in Figure 1.

| JAXA-QTS-2010/201<br>28 July 2025 | J A X A Parts Specification | Page | - 11 - |

|-----------------------------------|-----------------------------|------|--------|

|-----------------------------------|-----------------------------|------|--------|

## 3.1.3 Pin Material

The pin material for center 8x8 terminal shall be the solder ball content of high-temperature solder (Sn10/Pb90). The pin material for all terminals except center 8x8 terminal shall be the solder ball content of eutectic solder (Sn63/Pb37).

#### 3.1.4 Block Diagram and Pin-Outs

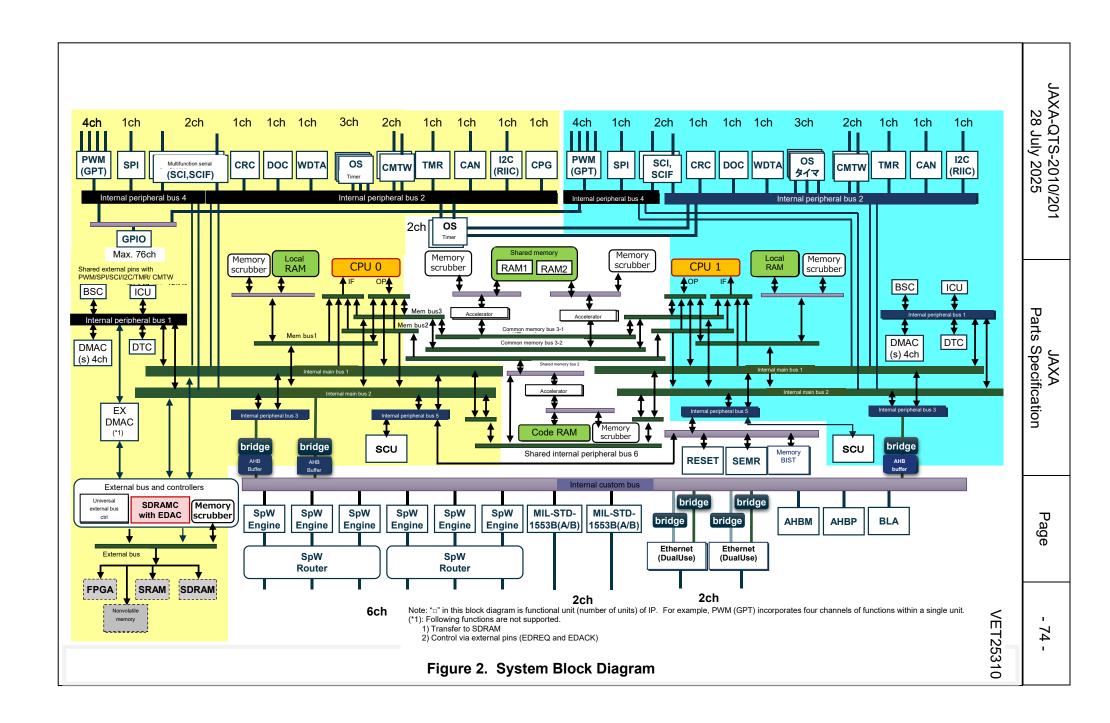

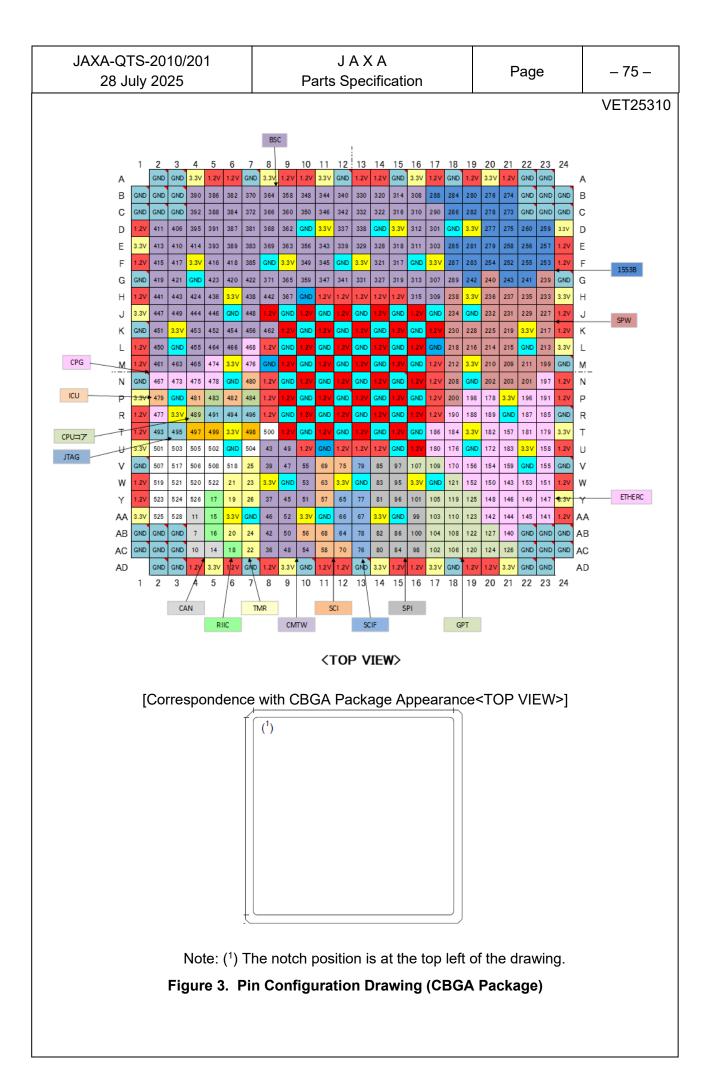

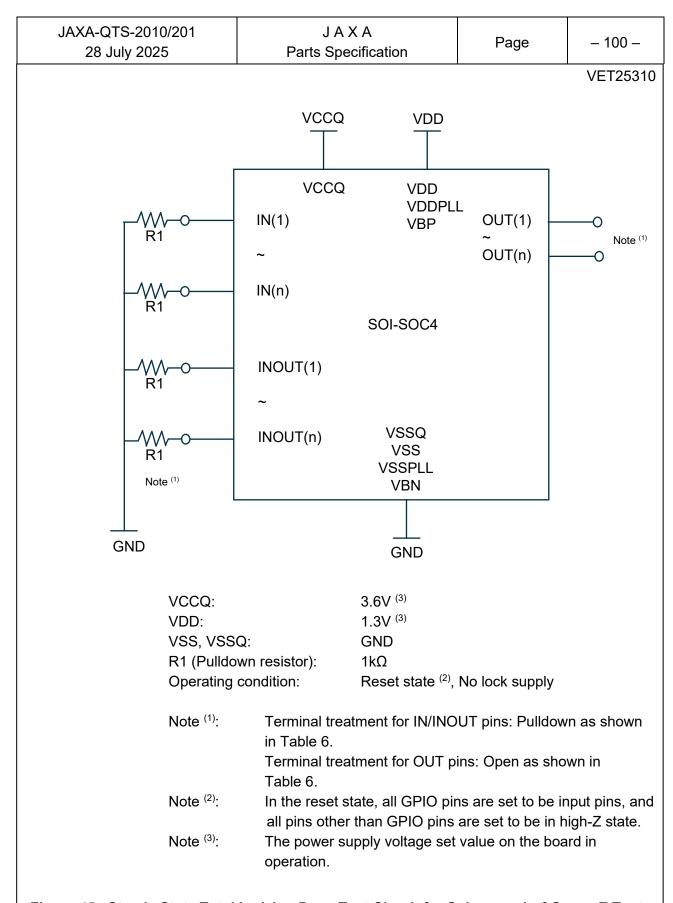

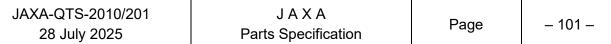

The block diagram of ICs shall be in accordance with Figure 2 and the pin-outs shall be as specified in Table 6 and Figure 3.

#### 3.1.5 Electrical Characteristics

The electrical characteristics shall be in accordance with Tables 7 and 8.

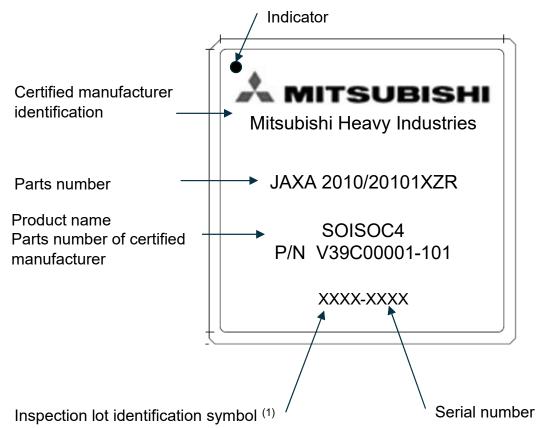

# 3.2 Marking

Marking on the products shall be as specified in paragraph G.3.4, Appendix G of JAXA-QTS-2010. An example is shown in Figure 4.

#### 3.3 Certification

The manufacturer shall acquire certification in accordance with paragraph G.3.1, Appendix G of JAXA-QTS-2010 and paragraph 3.4.1.10 of JAXA-QTS-2000.

# 3.4 Quality Assurance Program

Quality assurance program shall be in accordance with paragraph G.3.2, Appendix G of JAXA-QTS-2010.

| JAXA-QTS-2010/201<br>28 July 2025 | J A X A<br>Parts Specification | Page | <b>– 12 –</b> |

|-----------------------------------|--------------------------------|------|---------------|

| ,                                 | ·                              |      |               |

#### 4. QUALITY ASSURANCE PROVISIONS

The quality assurance shall meet the requirements of this section and paragraph G.4, Appendix G of JAXA-QTS-2010.

#### 4.1 General Requirements

The general requirements shall be in accordance with paragraph 4.1 of JAXA-QTS-2010.

## 4.2 Functional Drawing Control

The functional drawing control shall be in accordance with paragraph G.4.1, Appendix G of JAXA-QTS-2010.

# 4.3 Incoming Materials Control

The incoming materials control shall be in accordance with paragraph G.4.2, Appendix G of JAXA-QTS-2010.

# 4.4 Manufacturing Process Control

Manufacturing process control shall be in accordance with paragraph G.4.3, Appendix G of JAXA-QTS-2010.

However, since the wafer is a catalog item, the requirements specified in items a) through g) of paragraph G.4.3.1, Appendix G of JAXA-QTS-2010 shall not be applied.

# 4.5 In-Process Inspection

The in-process inspection shall be in accordance with paragraph G.4.4, Appendix G of JAXA-QTS-2010.

## 4.6 Screening

The screening shall meet the requirements specified in this section and paragraph G.4.6, Appendix G of JAXA-QTS-2010.

## 4.6.1 Screening Items and Conditions

Screening items and conditions for the ICs defined in this specification shall be as specified in Table 9.

#### 4.6.2 Electrical Parameters to be Measured

At the pre burn-in and final electrical parameters test of the screening test, all parameters included in the following subgroups, among those shown in Table 10 shall be measured.

| JAXA-QTS-2010/201 | JAXA                | Page  | <b>– 13 –</b> |

|-------------------|---------------------|-------|---------------|

| 28 July 2025      | Parts Specification | r ago | 10            |

Pre burn-in electrical parameter test Subgroups 1 and 7

Post burn-in electrical parameter test Subgroups 1 and 7

Final electrical parameter test Subgroups 1, 2, 3, 7, 8, 9 10,

and 11

Electrical parameter test after eutectic solder ball

attach

Subgroups 1,7, and 11

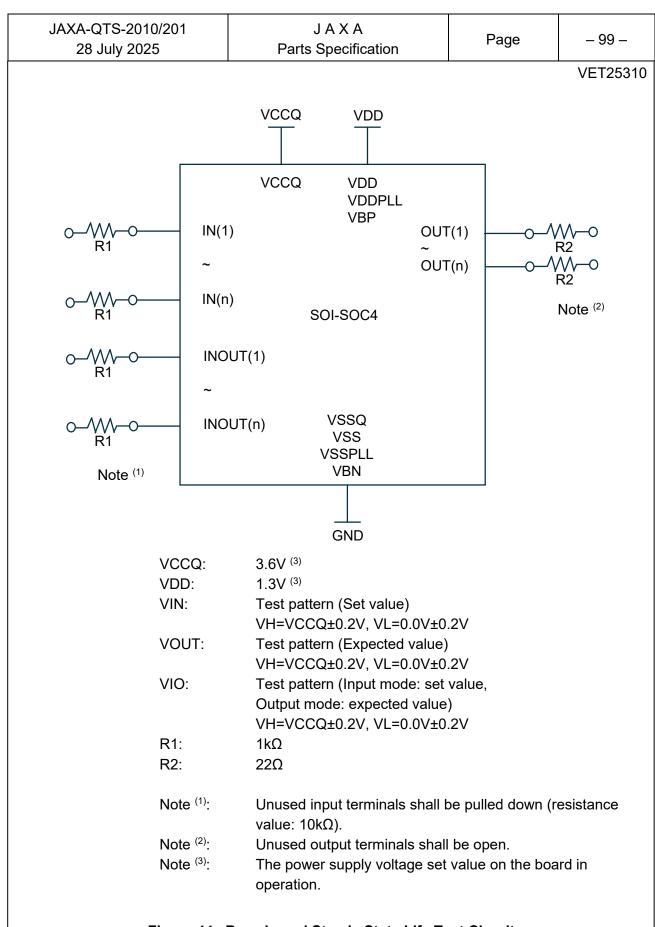

4.6.3 Burn-In Test Circuit

The burn-in test in the screening test shall be performed using the circuits shown in Figure 44.

4.6.4 Delta Limits

The delta limits for the burn-in test shall be as shown in Table 19.

4.7 Qualification Test for JAXA-developed Parts and Quality Conformance Inspection

The qualification test for JAXA-developed parts and quality conformance inspection shall meet the requirements specified in paragraphs G.4.5 and G.4.7, Appendix G of JAXA-QTS-2010, respectively.

However, when lot certification for wafer (specified in CCA-115025A) is applied to quality conformance inspection, other requirements specified in this section shall also apply.

4.7.1 Test/Inspection Items and Conditions

Test/inspection items and conditions for the ICs defined in this specification shall be as specified in Tables 10 through 14.

4.7.2 Electrical Parameters to be Measured

In the qualification test for JAXA-developed parts and quality conformance inspection, all electrical parameters included in the following subgroups specified in Tables 10 through 14 shall be measured.

Group C test, subgroup 1(c) Subgroups 1, 2, 3, 7, 8, 9, 10, and 11

Group C test, subgroup 2(d) Subgroups 1, 2, and 3

Group C test, subgroup 3(b) Subgroup 1

Group D test, subgroup 1(f) Subgroup 1

Group D test, subgroup 2(e) Subgroup 1

Group E test, subgroup 1(b) Subgroups 1, 7, and 9

| JAXA-QTS-2010/201<br>28 July 2025 | J A X A<br>Parts Specification | Page | <b>– 14</b> – |

|-----------------------------------|--------------------------------|------|---------------|

|-----------------------------------|--------------------------------|------|---------------|

Group E test, subgroup 2(b)

Subgroups 1, 7, and 9

#### 4.7.3 Exemption of Tests and Inspections

The tests or inspections may be exempted as specified in paragraph G.4.7.1.1, Appendix G of JAXA-QTS-2010 or when one of the following conditions is met.

a) Exemption of group A test

When the test items of the final electrical parameters of the screening test is the same as those of the group A test, the group A test may be exempted for the inspection lot if the lot passed the final electrical parameter test and if failed products were removed.

Exemption of group E tests

Group E tests may be exempted when the radiation hardness is not required for the ICs in the same inspection lot. In this case, the radiation hardness designator "R" shall not be marked on the ICs.

# 4.8 Long-Term Storage

4.8.1 Disposition of Products Stored for a Long-Term at the Manufacturer's Site

Disposition of products stored for a long-term at the manufacturer's site shall be in

accordance with paragraph G.4.8, Appendix G of JAXA-QTS-2010.

## 4.8.2 Storage by Purchasers

The storage conditions at purchaser's sites shall be as follows.

- a) Ambient temperature: +15°C to +35°C

- b) Relative humidity: No more than 35% (The ICs shall be stored in a desiccator to prevent the formation of oxide on the surface of the solder balls).

- c) Pressure: 86kPa to 106kPa

- d) Others: Vibration and shock shall not be applied.

# 4.9 Change of Tests and Inspections

# 4.9.1 Inspection of Wafer Lot

The manufacturer shall purchase wafers in conformance with the manufacturer's specifications (catalog) and shall verify that the wafers are in accordance with the specifications at item a) "Incoming inspection". Upon confirmation of wafer compliance with the specifications, those wafers that have passed the evaluation outlined in item b) "Post-Incoming Inspection Evaluation" shall be forwarded to the backside grinding process.

- a) Incoming inspection

- 1) Part number

- 2) Number of wafers

- 3) WAT (Wafer Acceptance Test) measurement results

- 4) Visual inspection results

| JAXA-QTS-2010/201 | JAXA                | Dawa | 45     |

|-------------------|---------------------|------|--------|

| 28 July 2025      | Parts Specification | Page | – 15 – |

b) Post-incoming inspection evaluation

- 1) WAT measurement at power supply voltage  $(V_{DD}) = 1.2V$

- 2) Characteristics evaluation of the elements of resistors, capacitors and transistors

- 3) Function evaluation of high density SRAM

- 4) Function and performance evaluation of Multi-Core Processor

## 4.9.2 Screening

The following changes have been made to the screening test specified in Table B-1 of JAXA-QTS-

a) Stabilization bake

This test has been substituted with the pre-sealing stabilization bake, since it is a seam weld, no high temperatures are applied to the ICs during sealing and since eutectic solder ball attach is performed after sealing but at a temperature equivalent to the soldering temperature.

- b) Radiographic inspection

- Screening before qualification test for JAXA-developed parts

While JAXA-QTS-2010 specifies that radiographic inspection shall be performed

from two views, the inspection have been changed to a total of three views: one

upward view and two lateral views, taking into account the internal structure of

the package.

- 2) Screening before quality conformance inspection

While JAXA-QTS-2010 specifies that radiographic inspection shall be performed

from two views, screening results prior to the qualification test for JAXAdeveloped parts indicate that wire bending and foreign materials can be

inspected from the one upward view alone. Therefore, radiographic inspection in

the lateral views (X1 and Z1 directions) is omitted, and the inspection has

perform the one upward view (Y2 direction) only.

- c) Reverse bias burn-in test and interim (post reverse bias burn-in) electrical parameter test

Reverse bias burn-in test and interim (post reverse bias burn-in) electrical parameter test shall not be performed because the I/O terminals have protective diodes.

- d) Final electrical parameter test

- In order to prevent IC socket contact marks from adhering to the solder balls of the package, final electrical parameter tests (at room temperature, high temperature and low temperature) shall be performed prior to the eutectic solder ball attach. For the electrical parameter test at room temperature, since the test conditions are identical to those for the post burn-in electrical parameter test (at room temperature), so the results from that test may be applied.

- e) Seal

- Eutectic solder balls shall be attached to the package between the final electrical parameter test and seal. Therefore, seal shall be performed after applying thermal conditions at the eutectic solder ball attach.

- f) Electrical parameter test after eutectic solder ball attach

With the change in the sequence of final electrical parameter tests to precede seal,

VET25310

an additional electrical parameter test at "room temperature only" shall be performed after seal.

## 4.9.3 Qualification Test for JAXA-developed Parts

#### 4.9.3.1 Group A Test

The following changes have been made to the group A test specified in Table C-1 of JAXA-QTS-2010.

# a) Subgroups 1 to 11

Since subgroups 1 to 11 tests are conducted in conjunction with the final electrical parameter screening test, the tests shall not be performed repeatedly.

## 4.9.3.2 Group B Test

The following changes have been made to the group B test specified in Table C-2 of JAXA-QTS-2010.

# a) Subgroup 2

1) Resistance to solvents

Hand pressure measurement shall not be performed during brushing. For paragraph 3.1, "Optional procedure for the fourth group", test method 2015 of MIL-STD-883, immersion shall be used, and chemical application by spray shall not be performed.

2) Verification of glassivation layer integrity

If there are any doubts with regard to the glassivation layer on the chip

surface during the "Internal Visual and Mechanical" in Subgroup 2,

verification of glassivation layer integrity shall be performed.

## b) Subgroup 3

1) Radiographic inspection

Radiographic inspection shall be added to inspect void(s) at the joint area between the solder ball and the package electrode.

2) Solderability

Since the requirements for solderability of BGAs are not specified in JAXA-QTS-2010, the requirements for solderability shall be changed as follows. The preconditioning condition shall be "155°C, Dry Bake for 4 hours," based on the long-term storage environment (Section 4.8) as a desiccator, applying Table 3-3 "Condition Category E" of item h), paragraph 2.1 of J-STD-002E.

- Evaluation item: Wettability of solder balls.

- Test method: MIL-STD-883L TM2003.10 BGA

### c) Subgroup 4

1) Lead integrity

While requirements for leads are specified in JAXA-QTS-2010, the requirements for BGA are not specified. For BGA, the lead integrity is substituted by the solder ball pull test in accordance with JESD22-B115A. Since acceptance criteria for solder ball pull test strength are not specified in

| JAXA-QTS-2010/201 | JAXA                | Dogo | 47   |

|-------------------|---------------------|------|------|

| 28 July 2025      | Parts Specification | Page | -17- |

JESD22-B115A, the following values, which were defined based on the results of the development of small packages for space use, shall be specified as the requirement for acceptance criteria.

- Eutectic solder balls: Minimum 40.0MPa

- High temperature solder balls: Minimum 19.7MPa

## 2) Seal

Seal shall not be performed because the external leads do not penetrate through the package.

# 4.9.3.3 Group C Test

The following changes have been made to the group C tests specified in Table C-3 of JAXA-QTS-2010.

# a) Subgroup 1

1) Steady state life test

When steady state life test conditions are set to +125°C for 2000 hours (double the standard 1000 hours), based on the LTPD concept, the sample size for the qualification test for JAXA-developed parts may be half of the LTPD5 requirement. If the sample size includes a decimal fraction, the sample size shall be rounded up.

# b) Subgroup 2

1) Constant acceleration

Test conditions shall apply condition A (5000G), test method 2001 of MIL-STD-883L.

#### 4.9.3.4 Group D Test

The following change has been made to the group D tests specified in Table C-4 of JAXA-QTS-2010.

#### a) Subgroup 4

1) Short circuit verification test

Since it was verified that wire short circuits did not occur based on evaluation results using an engineering model with the same wire bonding conditions as the product, this test shall be exempted.

## 4.9.3.5 Group E Test

For the same wafer lot, if Group E tests have been performed on one inspection lot, the remaining inspection lots may be exempted from all Group E tests.

## 4.9.4 Quality Conformance Inspection

For the inspections specified in Appendixes C and D of JAXA-QTS-2010, the changes specified in paragraph 4.9.3 shall also apply to this section. Other change items except those specified in paragraph 4.9.3 are as follows.

| JAXA-QTS-2010/201<br>28 July 2025 | J A X A Parts Specification | Page | - 18 <b>-</b> |

|-----------------------------------|-----------------------------|------|---------------|

|-----------------------------------|-----------------------------|------|---------------|

# 4.9.4.1 Group B Test

# a) Subgroup 1

1) Internal gas analysis

When quality conformance inspection data from the same wafer lot as the inspection lot ICs are not applicable, the sample size shall be determined according to Level I in the table of Appendix C of JAXA-QTS-2010. (For reference, JAXA-QTS-2010 specifies that Level II in the table of Appendix shall be applied.)

# b) Subgroup 2

Trom Internal visual and mechanical inspection to Die shear test When quality conformance inspection data from the same wafer lot as the inspection lot ICs are not applicable, the sample size shall be determined according to Level I in the table of Appendix C of JAXA-QTS-2010. (For reference, JAXA-QTS-2010 specifies that Level II in the table of Appendix shall be applied.)

## c) Subgroup 4

Subgroup 4 tests shall be performed regardless the test status of the ICs in the inspection lot. The sample size shall be determined according to Level II in the table of Appendix C of JAXA-QTS-2010. (For reference, Appendix G of JAXA-QTS-2010 specifies that subgroup 4 tests may be exempted.)

#### 5. PREPARATION FOR DELIVERY

Preparation for delivery shall be in accordance with paragraph G.5, Appendix G of JAXA-QTS-2010.

#### 6. NOTES

Refer to the paragraph G.6, Appendix G of JAXA-QTS-2010.

#### 6.1 Definition of Terms

Definitions of terms shall be applied in accordance with paragraph 6.1 of JAXA-QTS-2010 and the following.

a) Wafer lot

The definition of term specified in item k), paragraph 6.1 of JAXA QTS-2010 shall be applied.

b) Production lot

Same as the inspection lot.

c) Inspection lot

The inspection lot consists of a single wafer lot.

#### 6.2 Application Datasheet

The manufacturer shall prepare the application data sheet in accordance with Appendix G of JAXA-QTS-2000 and register it with JAXA.

| JAXA-QTS-2010/201 JAXA 28 July 2025 Parts Specification Page - 19 - | JAXA-QTS-2010/201<br>28 July 2025 | J A X A<br>Parts Specification | Page | - 19 <b>-</b> |

|---------------------------------------------------------------------|-----------------------------------|--------------------------------|------|---------------|

|---------------------------------------------------------------------|-----------------------------------|--------------------------------|------|---------------|

# 6.3 Notes for Purchasers

Notes for purchasers shall be applied in accordance with paragraph 6.3 of JAXA-QTS-2010 and the following.

- a) The ICs shall be handled carefully to avoid damaging the solder balls.

During temporary storage while handling, place the package with the LID side facing down to protect the solder balls.

- b) The cap on the package surface is connected to GND.

- c) The solder ball attachment areas of IC package feature a dimple structure. Therefore, since the solder balls are not able to be removed completely, it is impossible to perform rework on the solder balls.

- d) Maximum number of reflow cycles shall be two.

J A X A Parts Specification

Page

**- 20 -**

VET25310

# Table 6. Pin-Outs and Functions (1/22)

| A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 | GND GND 3.3V 1.2V 1.2V GND 3.3V 1.2V 1.2V 1.2V 1.2V 3.3V GND 1.2V 1.2V     | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | -<br>-<br>-<br>-<br>-<br>-<br>-<br>- | direction        | capability | As noted | VSS, VSSQ VSS, VSSQ VCCQ VDD VDD VSS, VSSQ VCCQ VDD VDD |

|-----------------------------------------|----------------------------------------------------------------------------|-------------------------------------------|--------------------------------------|------------------|------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| A3 A4 A5 A6 A7 A8 A9 A10 A11 A12        | GND 3.3V 1.2V 1.2V GND 3.3V 1.2V 1.2V 3.3V GND 1.2V                        | -                                         | -<br>-<br>-<br>-<br>-<br>-           | -<br>-<br>-<br>- |            | As noted                                              | VSS, VSSQ VCCQ VDD VDD VSS, VSSQ VCCQ VDD VDD           |

| A4 A5 A6 A7 A8 A9 A10 A11 A12           | 3.3V<br>1.2V<br>1.2V<br>GND<br>3.3V<br>1.2V<br>1.2V<br>3.3V<br>GND<br>1.2V | -                                         | -<br>-<br>-<br>-<br>-                | -<br>-<br>-<br>- |            | As noted                                                       | VCCQ VDD VDD VSS, VSSQ VCCQ VDD VDD                     |

| A5 A6 A7 A8 A9 A10 A11 A12              | 1.2V<br>1.2V<br>GND<br>3.3V<br>1.2V<br>1.2V<br>3.3V<br>GND<br>1.2V         | -<br>-<br>-<br>-<br>-<br>-<br>-           | -<br>-<br>-<br>-                     | -<br>-<br>-<br>- |            | As noted                                                                | VDD VDD VSS, VSSQ VCCQ VDD VDD                          |

| A6 A7 A8 A9 A10 A11 A12                 | 1.2V<br>GND<br>3.3V<br>1.2V<br>1.2V<br>3.3V<br>GND<br>1.2V                 | -<br>-<br>-<br>-<br>-<br>-                | -<br>-<br>-<br>-                     | -<br>-<br>-<br>- |            | As noted As noted As noted As noted As noted                                                                                  | VDD VSS, VSSQ VCCQ VDD VDD                              |

| A7<br>A8<br>A9<br>A10<br>A11<br>A12     | GND 3.3V 1.2V 1.2V 3.3V GND 1.2V                                           | -<br>-<br>-<br>-<br>-                     | -<br>-<br>-                          |                  |            | As noted As noted As noted As noted                                                                                           | VSS, VSSQ<br>VCCQ<br>VDD<br>VDD                         |

| A8<br>A9<br>A10<br>A11<br>A12           | 3.3V<br>1.2V<br>1.2V<br>3.3V<br>GND<br>1.2V                                | -<br>-<br>-<br>-<br>-                     | -<br>-<br>-                          |                  |            | As noted As noted As noted                                                                                                    | VCCQ<br>VDD<br>VDD                                      |

| A9<br>A10<br>A11<br>A12                 | 1.2V<br>1.2V<br>3.3V<br>GND<br>1.2V                                        | -<br>-<br>-<br>-                          | -                                    | -                |            | As noted As noted                                                                                                             | VDD<br>VDD                                              |

| A10<br>A11<br>A12                       | 1.2V<br>3.3V<br>GND<br>1.2V                                                | -<br>-<br>-<br>-                          | -                                    | -                |            | As noted                                                                                                                      | VDD                                                     |

| A11<br>A12                              | 3.3V<br>GND<br>1.2V                                                        | -<br>-<br>-                               | -                                    | -                |            |                                                                                                                               |                                                         |

| A12                                     | GND<br>1.2V                                                                |                                           | -                                    | -                |            |                                                                                                                               | 1/0-0-0                                                 |

|                                         | 1.2V                                                                       | -                                         | _                                    | i l              |            | As noted                                                                                                                      | VCCQ                                                    |

| A13                                     |                                                                            | _                                         |                                      | -                |            | As noted                                                                                                                      | VSS, VSSQ                                               |

|                                         | 1.2V                                                                       |                                           | -                                    | -                |            | As noted                                                                                                                      | VDD                                                     |

| A14                                     |                                                                            | -                                         | -                                    | -                |            | As noted                                                                                                                      | VDD                                                     |

| A15                                     | GND                                                                        | -                                         | -                                    | -                |            | As noted                                                                                                                      | VSS, VSSQ                                               |

| A16                                     | 3.3V                                                                       | -                                         | -                                    | -                |            | As noted                                                                                                                      | VCCQ                                                    |

| A17                                     | 1.2V                                                                       | -                                         | -                                    | -                |            | As noted                                                                                                                      | VDD                                                     |

| A18                                     | GND                                                                        | -                                         | -                                    | -                |            | As noted                                                                                                                      | VSS, VSSQ                                               |

| A19                                     | 1.2V                                                                       | -                                         | -                                    | -                |            | As noted                                                                                                                      | VDD                                                     |

| A20                                     | 3.3V                                                                       | -                                         | -                                    | -                |            | As noted                                                                                                                      | VCCQ                                                    |

| A21                                     | 1.2V                                                                       | -                                         | -                                    | -                |            | As noted                                                                                                                      | VDD                                                     |

| A22                                     | GND                                                                        | -                                         | -                                    | -                |            | As noted                                                                                                                      | VSS, VSSQ                                               |

| A23                                     | GND                                                                        | -                                         | -                                    | -                |            | As noted                                                                                                                      | VSS, VSSQ                                               |

| B1                                      | GND                                                                        | -                                         | -                                    | -                |            | As noted                                                                                                                      | VSS, VSSQ                                               |

| B2                                      | GND                                                                        | -                                         | -                                    | -                |            | As noted                                                                                                                      | VSS, VSSQ                                               |